CPU Interface Design Considerations

Layout Instructions

Copyright © 2002 Marvell

CONFIDENTIAL

Doc. No. MV-S300165-00, Rev. A

May 21, 2002, Preliminary

Document Classification: Proprietary Information

Page 105

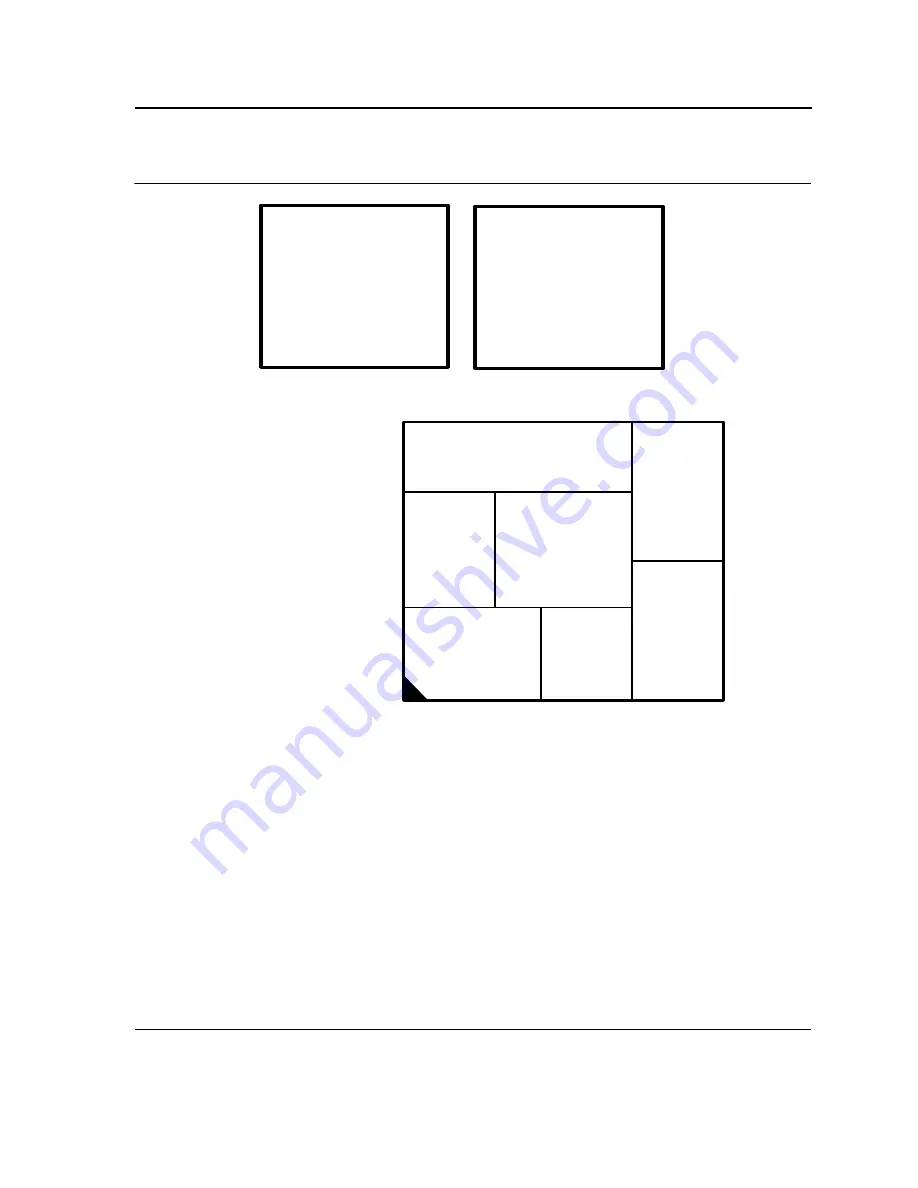

Figure 57: Layout for a Single GT-64260A to Multiple CPUs

The placement for multi-GT mode depends on the number of GT-64260A devices and interfaces used on each one

of them.

Depending on the system configuration and timing simulation, parallel termination on the bi-directional signals can

be placed near the CPUs or the GT-64260As.

14.5.2 Routing

The CPU interface traces must be 55 to 65 Ohm impedance.

The CPU and GT-64260A clocks (see section

Section 19. "Clocks" on page 143

) must be routed on separate lay-

ers from the other signals.

The point-to-multipoint topology signals must be routed in a "V" or "T" shape.

GT-64260A

CPU interface

PCI0

PCI1

SDRAM

Comm.

Device

A B C D . . .

.

.

.

4

3

2

1

CPU0

CPU1