Panel PC USER’S MANUAL

Intel Platform, High Performance PPC

31

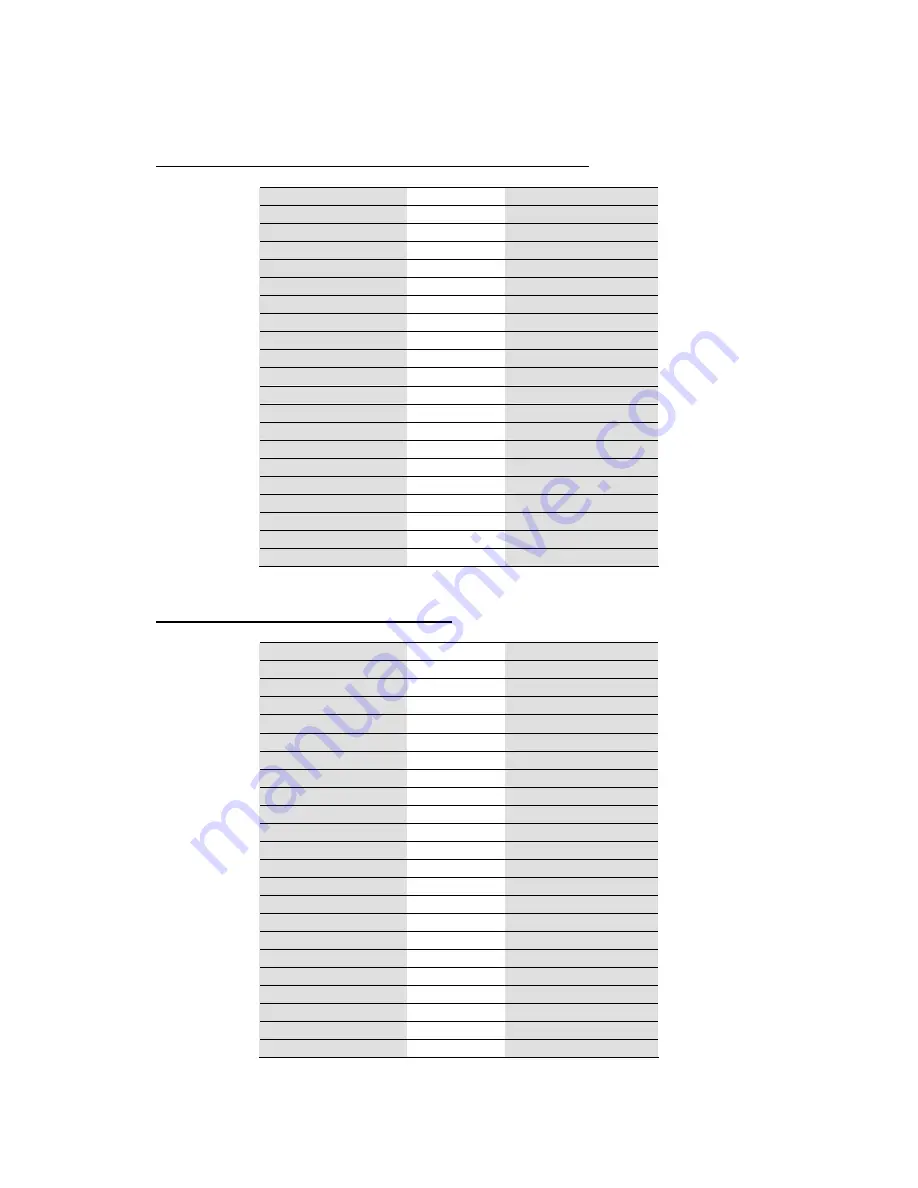

3.3.16 Primary and Secondary IDE Connectors (J18, J19)

Signal PIN

Signal

Reset IDE

1

2

Ground

Host data 7

3

4

Host data 8

Host data 6

5

6

Host data 9

Host data 5

7

8

Host data 10

Host data 4

9

10

Host data 11

Host data 3

11

12

Host data 12

Host data 2

13

14

Host data 13

Host data 1

15

16

Host data 14

Host data 0

17

18

Host data 15

Ground 19

20

Protect pin

DRQ0 21

22

Ground

Host IOW

23

24

Ground

Host IOR

25

26

Ground

IOCHRDY 27

28

Host ALE

DACK0 29

30

Ground

IRQ14 31

32

No connect

Address 1

33

34

No connect

Address 0

35

36

Address 2

Chip select 0

37

38

Chip select 1

Activity 39

40

Ground

3.3.17 Secondary IDE Connector (J19)

Signal PIN

Signal

Reset IDE

1

2

Ground

Host data 7

3

4

Host data 8

Host data 6

5

6

Host data 9

Host data 5

7

8

Host data 10

Host data 4

9

10

Host data 11

Host data 3

11

12

Host data 12

Host data 2

13

14

Host data 13

Host data 1

15

16

Host data 14

Host data 0

17

18

Host data 15

Ground 19

20

Key

DRQ0 21

22

Ground

Host IOW

23

24

Ground

Host IOR

25

26

Ground

IOCHRDY 27

28

Host ALE

DACK0 29

30

Ground

IRQ14 31

32

No connect

Address 1

33

34

No connect

Address 0

35

36

Address 2

Chip select 0

37

38

Chip select 1

Activity 39

40

Ground

Vcc 41

42

Vcc

Ground 43

44

N.C.