23

Terminations

Terminations

3

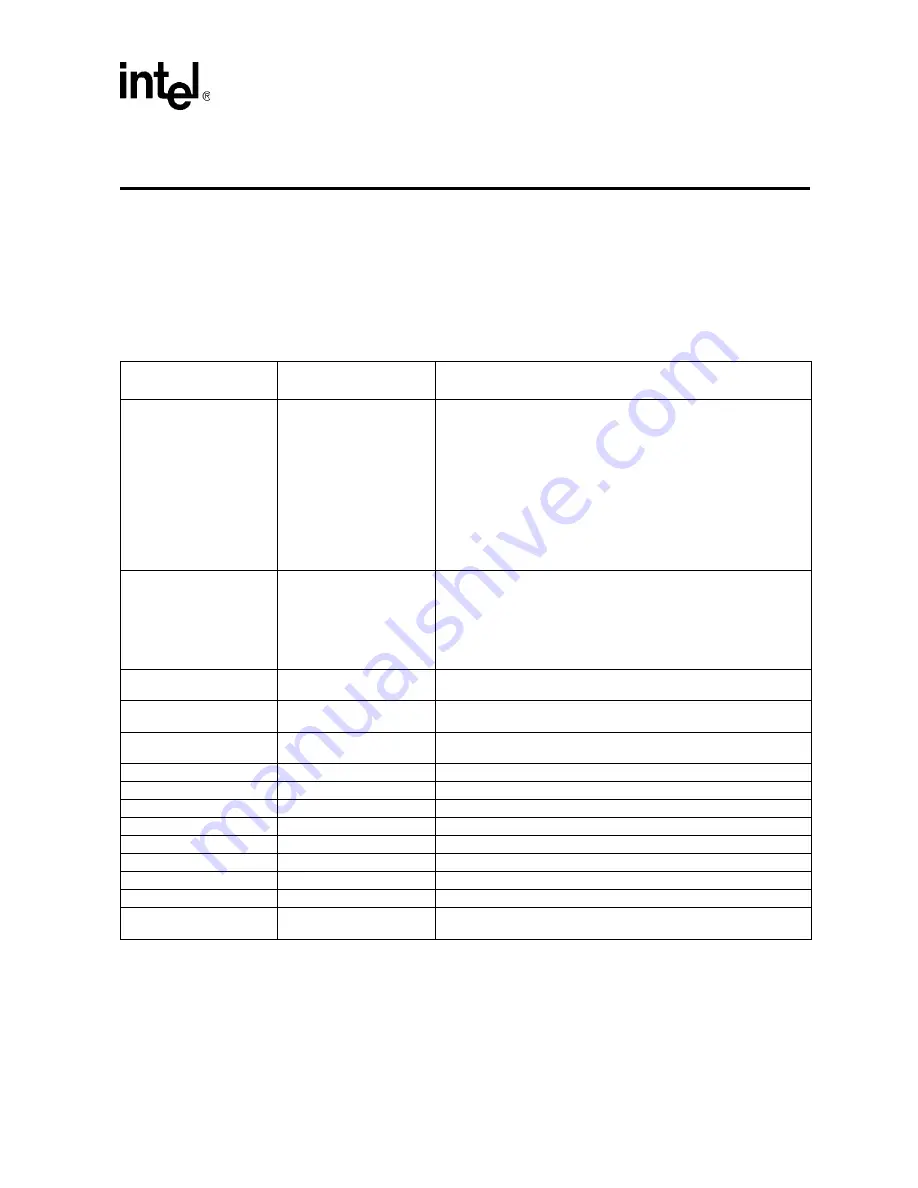

This chapter provides the recommended pull-up and pull-down terminations for a 80331 layout.

lists these 80331 termination values. On a motherboard, the

PCI Local Bus Specification

,

Revision 2.3 requires that the PCI signals provide the termination resistors. Pull-ups on the PCI

signals are not required with PCIODT_EN = 1 (enabled), because they are implemented on the die.

Refer to the

for more information.

Table 3.

Terminations: Pull-up/Pull-down (Sheet 1 of 4)

Signal

Pull-up or Pull-down

Resistor Value (in Ohms)

Comments

PWRDELAY

If battery backup is

implemented:

•

1.5 K pull-up to 3.3 V is

required on

PWRDELAY.

Battery Backup not

implemented:

•

This pin can be

permanently pulled low

with a 1.5K pull-down

TRST#

1.5K pull-down*

NOTES:

•

Alternatively tied to

P_RST#

refer to

for more information about using with a

ICE.

•

When not used this signal is be tied to GND.

•

This pin has an internal pull-up.

TMS

NC when not being used

(has internal pull-up)

TDI

NC when not being used

(has internal pull-up)

TCK

1.5K pull-down when not

used

GPIO[0]/U0_RXD

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

GPIO[1]/U0_TXD

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

GPIO[2]/U0_CTS#

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

GPIO[3]/U0_RTS#

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

GPIO[4]/U1_RXD

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

GPIO[5]/U1_TXD

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

GPIO[6]/U1_CTS#

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

GPIO[7]/U1_RTS

8.2 K pull-up

Note:

GPIO[7:0]

initializes as inputs on assertion of

P_RST#

.

ARB_EN

(see comments)

This signal has been defeatured. Please refer to the Intel® 80331

Specification Update for more information.

Содержание 80331

Страница 1: ...Intel 80331 I O Processor Design Guide March 2005 Order Number 273823 003 ...

Страница 30: ...Intel 80331 I O Processor Design Guide Terminations 30 This Page Intentionally Left Blank ...

Страница 122: ...122 Intel 80331 I O Processor Design Guide Memory Controller ...

Страница 130: ...Intel 80331 I O Processor Design Guide Peripheral Local Bus 130 This Page Intentionally Left Blank ...

Страница 136: ...Intel 80331 I O Processor Design Guide Power Delivery 136 This Page Intentionally Left Blank ...