[AK4493]

017012230-E-00

2017/12

- 69 -

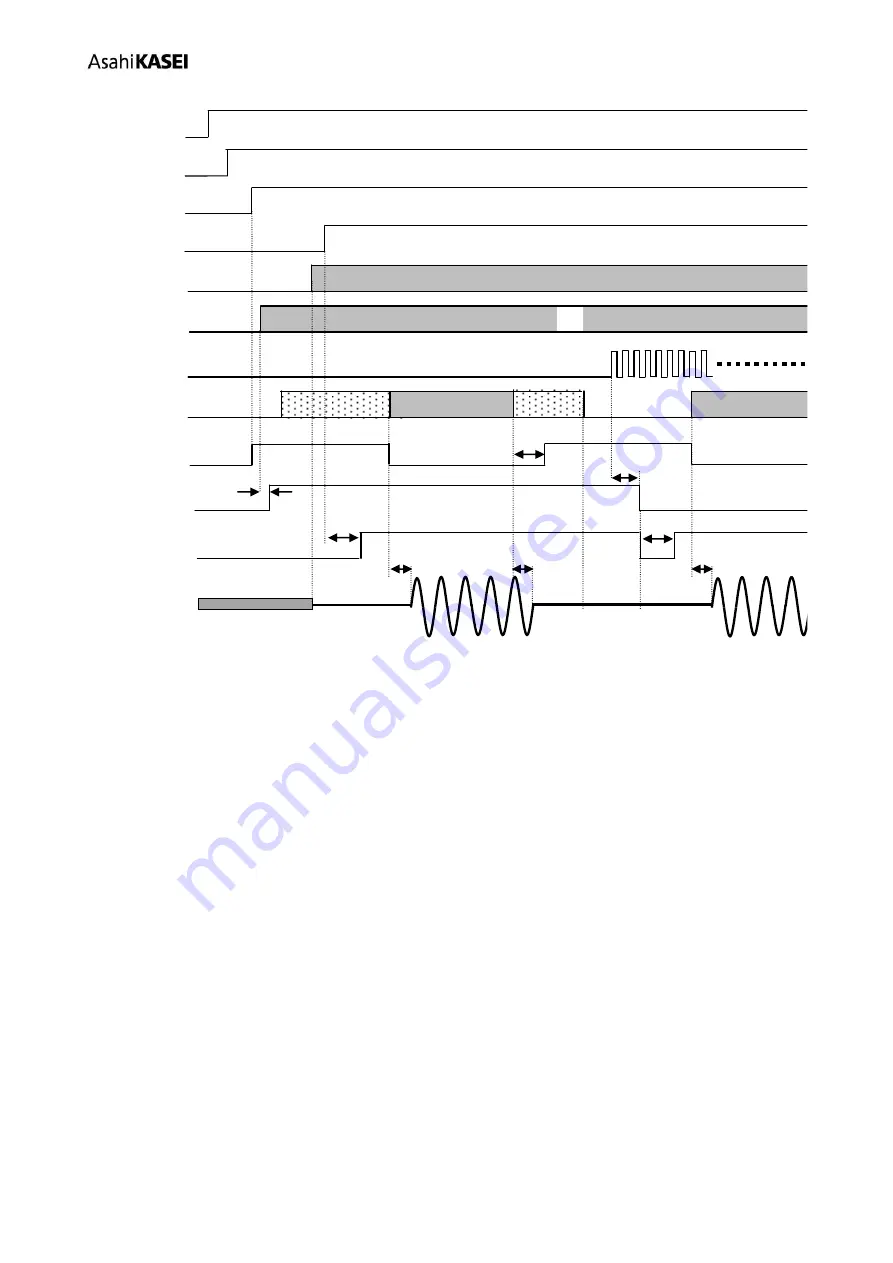

AOUT pin

RSTN bit

Internal RSTN bit

3~4/fs

PDN pin

BCK/DCLK pin

DINR/DSDR pin

ADPE bit

ADP bit

(Result of Auto DSD mode setting)

(2)

MCLK pin

DSD mode Detect

Operation Enable

WCK pin

EXDF data

DSD data

DSD zero

(4)

(7)

(3)

(3)

(5)

(5)

(6)

(6)

(8)

DSD zero

(9)

EXDF bit

(1)

Hi-z

“L”

“L”

“L”

Note

:

(1) Automatic mode switching between PCM/EXDF and DSD modes is enabled by setting ADPE bit =

“1”

after setting PDN pin

“L” → “H”. EXDF bit must be set before ADPE bit if setting EXDF bit = “1”.

(2) If RSTN bit is in default value

“0”, mode detection will start by setting ADPE bit = “1”.

(3) Mode detection is performed by monitoring input clock of the WCK and BCK/DCLK pins. It takes

256DCLK cycles for mode switching from EXDF to DSD mode, and takes 2WCK cycles for mode

switching from DSD to EXDF mode. Mode detection is executed even when there is no MCLK input.

(4) According to power-up sequence, reset is released when MCLK is input after setting RSTN bit=

“1”.

(5) The AK4493 starts mode detection when input data of both channels are continuously zero for the

period set by ADPT[1:0] bits, and it finishes mode detection when a data that is not zero is input.

(6) In DSD mode, analog output delay time becomes longer comparing with when setting ADPE bit =

“0”.

In this case, delay time depends on DDMT[1:0] bits setting.

(7) In EXDF mode, analog output delay time becomes 18/fs longer comparing with when setting ADPE

bit =

“0”.

(8) If DCLK input is stopped in DSD mode, the AK4493 stays in DSD mode and continues operation.

(9) If DSDR input is stopped in DSD mode, the AK4493 stays in DSD mode and continues operation. In

this case, full-scale data is input to the AK4493. Excessive signal output can be avoided by setting

DDM bit =

“1” enabling automatic mute function works when detecting DSD full-scale input.

Figure 55. Changing to EXDF Mode after Power-up In DSD Mode (EXDF bit =

“1”)