Chapter 5: IP Core Architecture

5–17

Completer Only Single Dword Endpoint

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

■

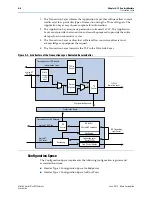

Bits [23:20] select the address translation table entry.

■

Bits [63:20] of the address translation table entry become PCI Express address bits

[63:20].

■

Bits [19:0] are passed through and become PCI Express address bits [19:0].

The address translation table is dynamically configured at run time. The address

translation table is implemented in memory and can be accessed through the CRA

slave module. Dynamic configuration is optimal in a typical PCI Express system

where address allocation occurs after BIOS initialization.

For more information about how to access the dynamic address translation table

through the CRA slave, refer to the

“Avalon-MM-to-PCI Express Address Translation

Table 0x1000–0x1FFF” on page 7–15

depicts the Avalon-MM-to-PCI Express address translation process.

Completer Only Single Dword Endpoint

The completer only single dword endpoint is intended for applications that use the

PCI Express protocol to perform simple read and write register accesses from a host

CPU. The completer only single dword endpoint is a hard IP implementation

available for Qsys systems, and includes an Avalon-MM interface to the Application

Layer. The Avalon-MM interface connection in this variation is 32 bits wide. This

endpoint is not pipelined; at any time a single request can be outstanding.

The completer-only single dword endpoint supports the following requests:

■

Read and write requests of a single dword (32 bits) from the Root Complex

Figure 5–8. Avalon-MM-to-PCI Express Address Translation

(1)

,

(2)

,

(3)

,

(4)

,

(5)

Notes to

(1)

N

is the number of pass-through bits.

(2)

M

is the number of Avalon-MM address bits.

(3)

P

is the number of PCI Express address bits.

(4)

Q

is the number of translation table entries.

(5)

Sp[1:0]

is the space indication for each entry.

PCIe Address Q-1

SpQ-1

Space Indication

PCI Express address from Table Entry

becomes High PCI Express address bits

PCI Express Address

High

Low

P-1

N N-1

0

Low address bits unchanged

Avalon-MM-to-PCI Express

Address Translation Table

(Q entries by P-N bits wide)

PCIe Address 0

Sp0

PCIe Address 1

Sp1

Avalon-MM Address

High

Slave Base

Address

Low

M-1

31

M

N N-1

0

Table updates from

control register port

High Avalon-MM Address

Bits Index table