MC96FR116C

November, 2018 Rev.1.8

115

0

Timer 3 is in normal operation

1

Timer 3 calculates the number of incoming carrier signals.

T2IR

Make T3 to calculate the number of incoming carrier signal if CAP3

bit in T3CR bit is not ‘1’.

0

Timer 2 is in normal operation

1

Timer 2 calculates the number of incoming carrier signals.

T3EDGE[1:0]

Select capture edge when T3 is used for envelop detection of

incoming carrier signal. These bits should be cleared to ‘00’ when

T3 operates in normal capture mode, or the WT output becomes

capture source of Timer 3. The T3IR bit should be cleared to ‘0’

also.

00

No capture

01

Falling edge

10

Rising edge

11

Both edge

T2EDGE[1:0]

Select capture edge when T2 is used for envelop detection of

incoming carrier signal. These bits should be cleared to ‘00’ when

T2 operates in normal capture mode, or the WT output becomes

capture source of Timer 2. The T2IR bit should be cleared to ‘0’

also.

00

No capture

01

Falling edge

10

Rising edge

11

Both edge

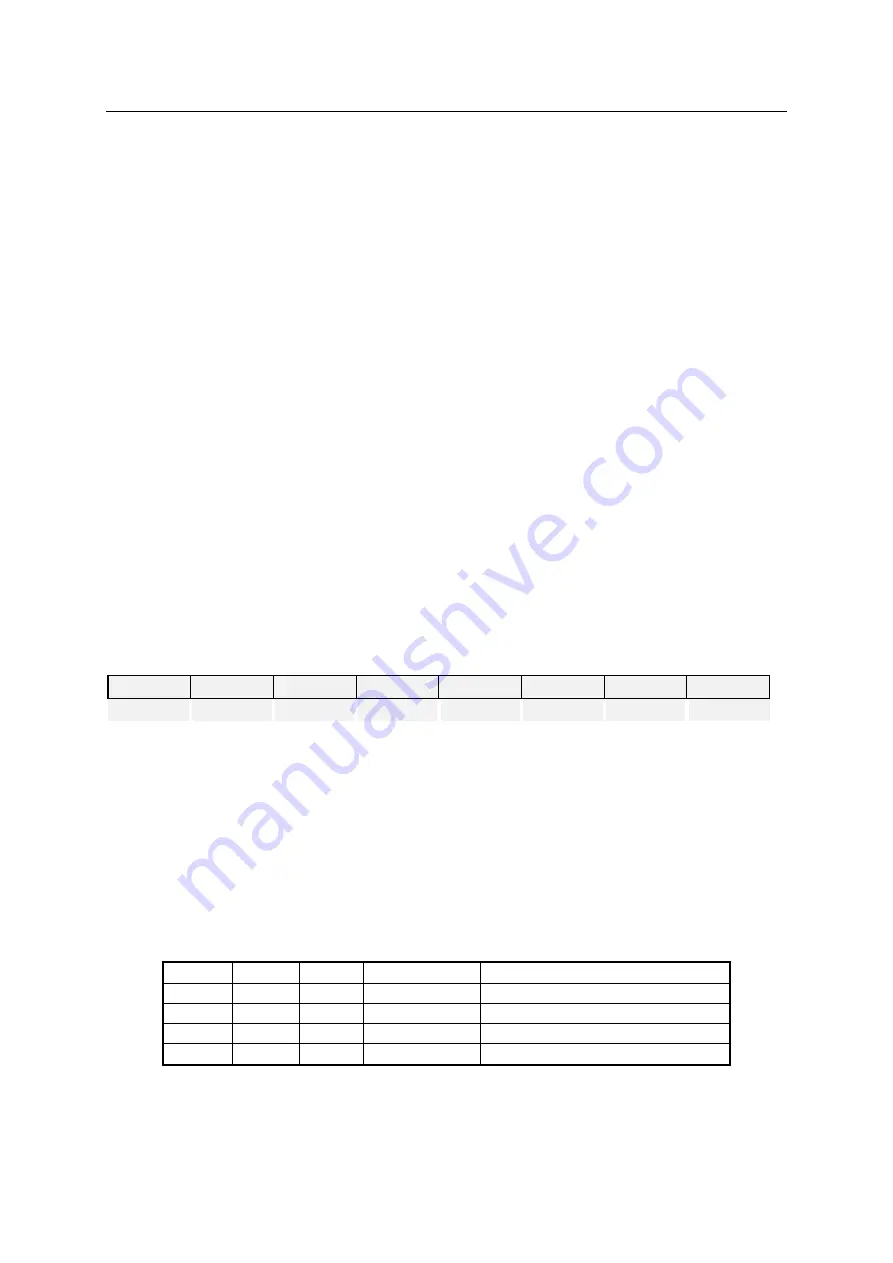

IRCC3 (IR Capture Control Register 3)

AF

H

7

6

5

4

3

2

1

0

-

-

-

-

-

-

IRPUDL1

IRPUDL0

R

R

R

R

R

R

R/W

R/W

Initial value : 00

H

IRPUDL[1:0]

Select the delay time of IR learning dynamic pull-up activation.

Refer to “Figure 11-28 Block Diagram of IR Learning” and “Figure

11-29 Timing Diagram of IR Learning”.

IRPUDL1 IRPUDL0

0

0

0.7us

0

1

1.0us

1

0

1.5us

1

1

2.0us

The next table shows register setting for Timer 2 and 3 for IR capture features.

IRCEN

CAP2(3)

T2(3)IR

T2(3)EDGE[1:0]

Timer 2(3) Operating Mode

0

0

0

XX

Normal 16-bit Counter

0

1

X

00

Normal 16-bit Capture

1

1

X

01, 10, 11

IR Capture (Envelop detect)

1

0

1

XX

Count IR Carrier

Table 11-12 Operating modes of Timer 2(3)