Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1

183

UG586 November 30, 2016

Chapter 1:

DDR3 and DDR2 SDRAM Memory Interface Solution

The parameters listed in

depend on the selected memory clock frequency,

memory device, memory configuration, and FPGA speed grade. The values for these

parameters are embedded in the

memc_ui_top

IP core and should not be modified in the

top-level.

RECOMMENDED:

Xilinx strongly recommends that the MIG tool be rerun for different configurations.

DIFF_TERM_REFCLK

“TRUE,” “FALSE”

Differential termination for IDELAY

reference clock input pins.

TEMP_MON_CONTROL

This option selects the device temperature

source for the Temperature Monitor feature

). Select "INTERNAL"

to direct the MIG tool to instantiate the XADC

and temperature polling circuit in the memory

interface top-level user design module. Select

"EXTERNAL" if the XADC is already instantiated

elsewhere in the design. In this case, the device

temperature must be periodically sampled and

driven onto the device_temp_i bus in the

memory interface top-level user design

module.

“INTERNAL”

“EXTERNAL”

Notes:

1. The lower limit (maximum frequency) is pending characterization.

2. Core initialization during simulation can be greatly reduced by using SIM_BYPASS_INIT_CAL. Three simulation modes are

supported. Setting SIM_BYPASS_INIT_CAL to FAST causes write leveling and read calibration to occur on only one bit per

memory device. This is then used across the remaining data bits. Setting SIM_BYPASS_INIT_CAL to SIM_INIT_CAL_FULL causes

complete memory initialization and calibration sequence occurs on all byte groups. SIM_BYPASS_INIT_CAL should be set to

SIM_INIT_CAL_FULL for simulations only. SIM_BYPASS_INIT_CAL should be set to OFF for implementation, or the core does

not function properly.

3. When set to NORM or RELAXED, ORDERING enables the reordering algorithm in the Memory Controller. When set to STRICT,

request reordering is disabled, which might limit throughput to the external memory device. However, it can be helpful

during initial core integration because requests are processed in the order received; the user design does not need to keep

track of which requests are pending and which requests have been processed.

4. This parameter is prefixed with the module name entered in the MIG tool during design generation. If the design is

generated with the module name as mig_7series_0, then IODELAY_GRP parameter name is "mig_7series_0_IODELAY_MIG."

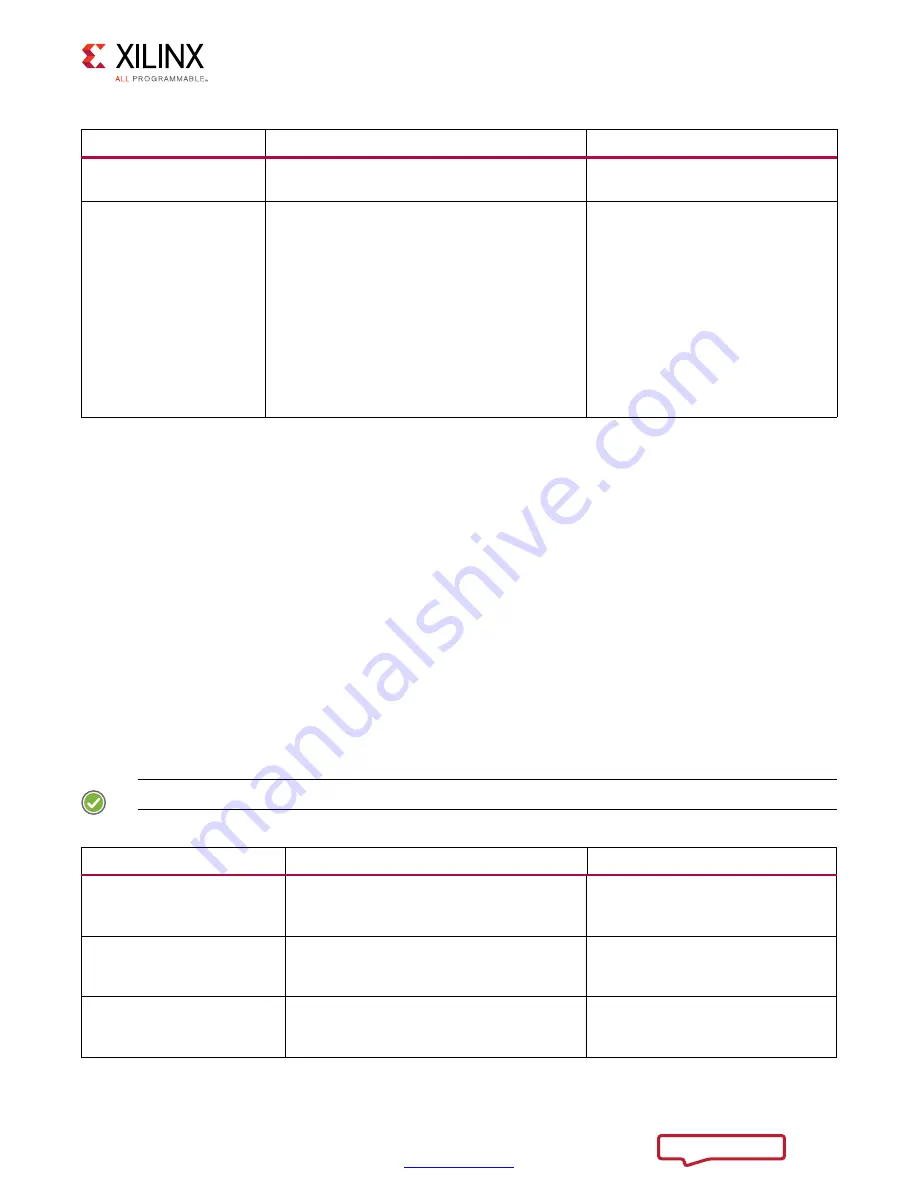

Table 1-64:

7 Series FPGA Memory Solution Configuration Parameters

(Cont’d)

Parameter

Description

Options

Table 1-65:

Embedded 7 Series FPGAs Memory Solution Configuration Parameters

Parameter

Description

Options

tFAW

This is the minimum interval of four active

commands.

This value, in picoseconds, is based

on the device selection in the MIG

tool.

tRRD

This is the ACTIVE-to-ACTIVE minimum

command period.

This value, in picoseconds, is based

on the device selection in the MIG

tool.

tRAS

This is the minimum ACTIVE-to-PRECHARGE

period for memory.

This value, in picoseconds, is based

on the device selection in the MIG

tool.