ZC706 Evaluation Board User Guide

61

UG954 (v1.5) September 10, 2015

Feature Descriptions

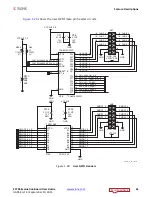

shows the user GPIO male pin header circuits.

X-Ref Target - Figure 1-28

Figure 1-28:

User GPIO Headers

PMOD1_0_LS

PMOD1_1_LS

PMOD1_2_LS

PMOD1_3_LS

PMOD1_4_LS

PMOD1_5_LS

PMOD1_6_LS

PMOD1_7_LS

PMOD1_0

PMOD1_1

PMOD1_2

PMOD1_3

PMOD1_4

PMOD1_5

PMOD1_6

PMOD1_7

HDR_2X6

VCC3V3

VCCA

A1

A2

A3

A4

A5

A6

A7

A8

OE

VCCB

B1

B2

B3

B4

B5

B6

B7

B8

GND

19

20

18

17

16

15

14

13

12

11

2

4

6

8

10

12

1

3

5

7

9

11

PMOD1_4

PMOD1_5

PMOD1_6

PMOD1_7

PMOD1_0

PMOD1_1

PMOD1_2

PMOD1_3

2

1

3

4

5

6

7

8

9

10

TSSOP_20

TCA6416APWR

U40

U16

GND

GND

UG954_c1_28_031715

R310

DNP

DNP

DNP

R330

0

1/10W

5%

R65

4.7

1/10W

5%

1

2

1

2

1

2

TXS0108E

C105

0.1UF

10V

X5R

C104

0.1UF

10V

X5R

J58

1

2

GND

1

2

GND

GND

PORT_EXPANDER_DDR3_SDA

PORT_EXPANDER_DDR3_SCL

NC

IIC_PMOD_0

IIC_PMOD_1

IIC_PMOD_2

IIC_PMOD_3

IIC_PMOD_4

IIC_PMOD_5

IIC_PMOD_6

IIC_PMOD_7

FMC_VADJ_ON_R_B

FMC_LPC_PRSNT_M2C_B

FMC_HPC_PRSNT_M2C_B

FMC_HPC_PG_M2C

XADC_MUX_ADDR0

XADC_MUX_ADDR1

XADC_MUX_ADDR2

PL_PWR_ON_R

HDR_2X6

VCC3V3_PS

VCCP

VCCI

SDA

SCL

ADDR

RESET_B

INT_B

GND

P00

P01

P02

P03

P04

P05

P06

P07

P10

P11

P12

P13

P14

P15

P16

P17

4

5

6

7

8

9

10

11

13

14

15

16

17

18

19

20

2

4

6

8

10

12

1

3

5

7

9

11

IIC_PMOD_4

IIC_PMOD_5

IIC_PMOD_6

IIC_PMOD_7

IIC_PMOD_0

IIC_PMOD_1

IIC_PMOD_2

IICPMOD_3

24

2

23

22

21

3

1

12

VCC3V3_PS

VCC3V3_PS

TCA6416APWR

C97

0.1UF

10V

X5R

C96

0.1UF

10V

X5R

J57

1

2

GND

1

2

GND

GND

GND

VADJ

VCC3V3