AXI Bridge for PCI Express v2.4

57

PG055 June 4, 2014

Chapter 3:

Designing with the Core

MSI Interrupt

When the

msi_enable

output pin indicates that the bridge has Endpoint MSI functionality

enabled (

msi_enable

= ‘1’), the

intx_msi_request

input pin is defined as MSI_Request

and can be used to trigger a Message Signaled Interrupt through a special MemWr TLP to

an external Root Port for PCIe on the PCIe side of the Bridge. The

intx_msi_request

input pin is positive-edge detected and synchronous to

axi_aclk_out

. The address and

data contained in this MemWr TLP are determined by an external Root Port for PCIe

configuration of registers within the integrated block for PCI Express. The

intx_msi_request

pin input is valid only when the bridge is operating in Endpoint mode

(C_INCLUDE_RC=0).

Additional MSI capability now supports multiple vectors on the Endpoint configuration of

the AXI Bridge for PCI Express core. Using the handshaking described here, an additional

input value specifies the vector number to send with the MSI MemWr TLP upstream to the

Root Port. This is specified on the input signal,

msi_vector_num

. This signal is (4:0), and

represents up to (32), the allowable MSI messages that can be sent from the Endpoint (and

what is enabled after configuration).

The bridge ignores any bits set on the

msi_vector_num

input signal, if they are not

allocated in the Message Control Register.

The Endpoint requests the number of message as specified in the design parameter (of the

AXI Bridge for PCI Express), C_NUM_MSI_REQ. Following specification requirements, this

parameter can be set up to 5. C_NUM_MSI_REQ represents the number of MSI vectors

requested. For example, C_NUM_MSI_REQ = 5 represents a request of 2

5

= 32 MSI vectors.

This parameter value, C_NUM_MSI_REQ is assigned to the Message Control Register field,

Multiple Message Capable, bits (3:1).

After configuration, the number of allocated MSI vectors is specified in the design output

port,

msi_vector_width

. This signal with width, (2:0), can only be values up to 5 (101),

representing 32 allocated MSI vectors for the Endpoint. Output values of 6 and 7; 110 and

111 are reserved. The

msi_vector_width

output signal is a direct correlation from the

value in the Multiple Message Enable field bits (6:4) of the Message Control Register as

shown in

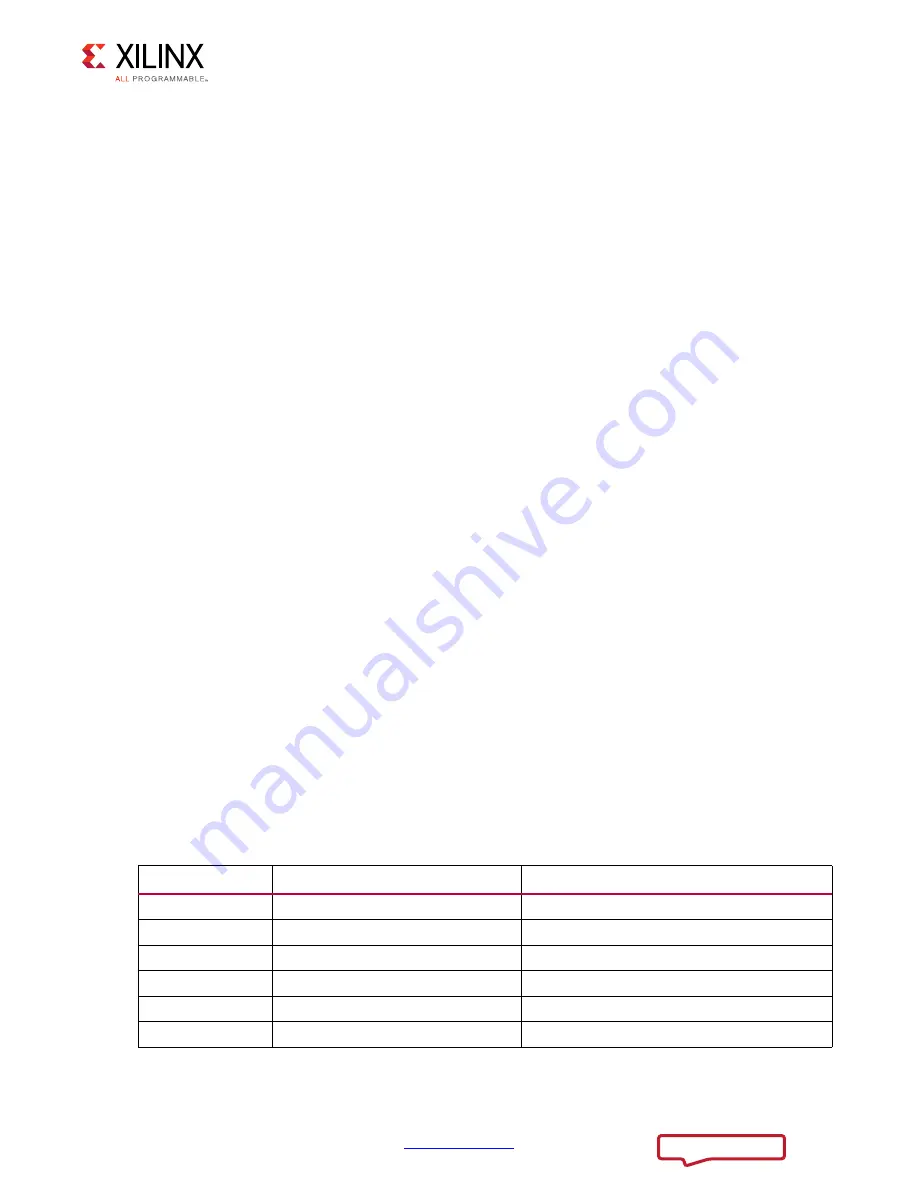

Table 3-5:

MSI Vectors Enabled in Message Control Register

Value

Number of Messages Requested

Output Signal, MSI_Vector_Width (2:0)

“000”

1

000

“001”

2

001

“010”

4

010

“011”

8

011

“100”

16

100

“101”

32

101