AXI Bridge for PCI Express v2.4

34

PG055 June 4, 2014

Chapter 2:

Product Specification

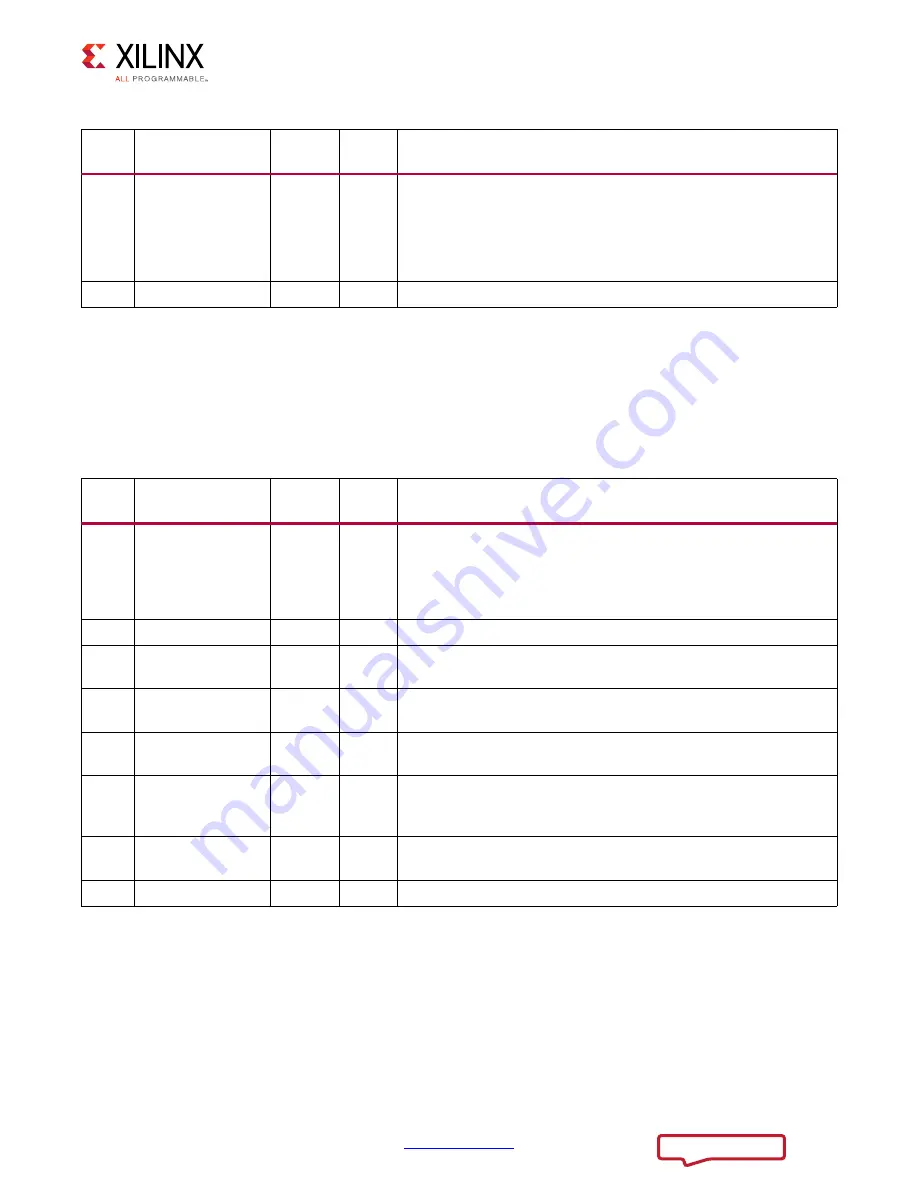

Root Port Status/Control Register (Offset 0x148)

The Root Port Status/Control register provides access to Root Port specific status and

control. This register is only implemented for Root Port cores. For non-Root Port cores,

reads return 0 and writes are ignored (described in

21:20 Directed Link

Change

RW

0

Directs LTSSM to initiate a link width and/or speed change.

• 00b: No change

• 01b: Force link width

• 10b: Force link speed

• 11b: Force link width and speed

31:22 Reserved

RO

0

Reserved

Table 2-15:

PHY Status/Control Register

(Cont’d)

Bits

Name

Core

Access

Reset

Value

Description

Table 2-16:

Root Port Status/Control Register

Bits

Name

Core

Access

Reset

Value

Description

0

Bridge Enable

RW

0

When set, allows the reads and writes to the AXIBARs to be

presented on the PCIe bus. Root Port software needs to write 1

to this bit when enumeration is done. AXI Enhanced PCIe Bridge

clears this location when link up to link down transition occurs.

Default is set to 0.

15:1

Reserved

RO

0

Reserved.

16

Error FIFO Not

Empty

RO

0

Indicates that the Root Port Error FIFO has data to read.

17

Error FIFO

Overflow

RW1C

0

Indicates that the Root Port Error FIFO overflowed and an error

message was dropped. Writing a 1 clears the overflow status.

18

Interrupt FIFO Not

Empty

RO

0

Indicates that the Root Port Interrupt FIFO has data to read.

19

Interrupt FIFO

Overflow

RW1C

0

Indicates that the Root Port Interrupt FIFO overflowed and an

interrupt message was dropped. Writing a 1 clears the overflow

status

27:20 Completion

Timeout

RW

0

Sets the timeout counter size for Completion Timeouts.

31:28 Reserved

RO

0

Reserved.