AXI Bridge for PCI Express v2.4

28

PG055 June 4, 2014

Chapter 2:

Product Specification

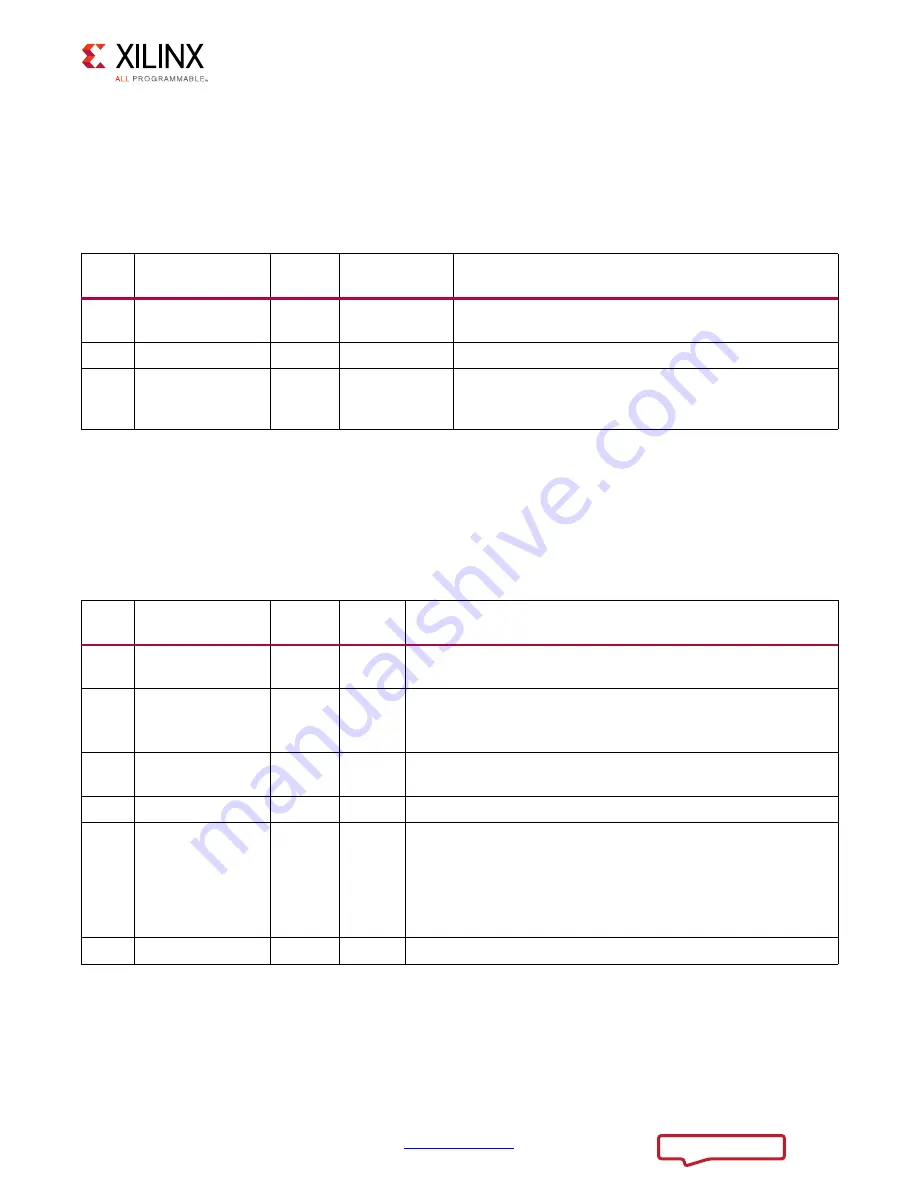

VSEC Header Register (Offset 0x12C)

The VSEC Header register (described in

) provides a unique (within a given vendor)

identifier for the layout and contents of the VSEC structure, as well as its revision and

length.

Bridge Info Register (Offset 0x130)

The Bridge Info register (described in

) provides general configuration

information about the AXI4-Stream Bridge. Information in this register is static and does

not change during operation.

Table 2-9:

VSEC Header Register

Bits

Name

Core

Access

Reset Value

Description

15:0

VSEC ID

RO

0x0001

ID value uniquely identifying the nature and format of

this VSEC structure.

19:16 VSEC REV

RO

0

Version of this capability structure. Hardcoded to

0h

.

31:20 VSEC Length

RO

0x038

Length of the entire VSEC Capability structure, in bytes,

including the VSEC Capability register. Hardcoded to

0x038

(56 decimal).

Table 2-10:

Bridge Info Register

Bits

Name

Core

Access

Reset

Value

Description

0

Gen2 Capable

RO

0

If set, indicates the link is Gen2 capable. Underlying integrated

block and Link partner support PCIe Gen2 speed.

1

Root Port Present

RO

0

Indicates the underlying integrated block is a Root Port when

this bit is set.

If set, Root Port registers are present in this interface.

2

Up Config

Capable

RO

Indicates the underlying integrated block is upconfig capable

when this bit is set.

15:3

Reserved

RO

0

Reserved

18:16 ECAM Size

RO

0

Size of Enhanced Configuration Access Mechanism (ECAM) Bus

Number field, in number of bits. If ECAM window is present,

value is between 1 and 8. If not present, value is 0. Total address

bits dedicated to ECAM window is 20+(ECAM Size).

The size of the ECAM is determined by the parameter settings

of C_BASEADDR and C_HIGHADDR.

31:19 Reserved

RO

0

Reserved