AXI Bridge for PCI Express v2.4

43

PG055 June 4, 2014

Chapter 3:

Designing with the Core

The

refclk

input must be provided at the frequency selected by the value of

c_ref_clk_freq

. This clock is used to generate the two output clocks and is also the

clock used to drive the AXI4 bus.

The AXI4-Lite interconnect clock

axi_ctl_aclk

is driven by

axi_ctl_aclk_out

. The

axi_ctl_aclk_out

clock is rising edge aligned and an integer division of the

axi_aclk_out

clock.

The output clock frequency is 62.5 Mhz for x1 gen1 64-bit AXI interface, and 125 Mhz for

the remaining configurations.

Resets

The AXI Bridge for PCI Express core is designed to be used with the Processing System Reset

module for generation of the

axi_areset

input. When using the Vivado IP integrator to

build a system, it is best to connect the

perstn

pin of the host connector for PCIe to the

Aux_Reset_In

port of the Processing System Reset module. The bridge does not use

perstn

directly. Also, the

mmcm_lock

output must be connected to the

dcm_locked

input of the Processing System Reset module to make sure that

axi_aresetn

is held

active for 16 clocks after

mmcm_lock

becomes active. See

Note:

Be sure to set the correct polarity on the

aux_reset_in

signal of the proc_sys_reset ip

block. when

PERSTN

is active-Low, set the parameter as follows:

PARAMETER C_AUX_RESET_HIGH = 0

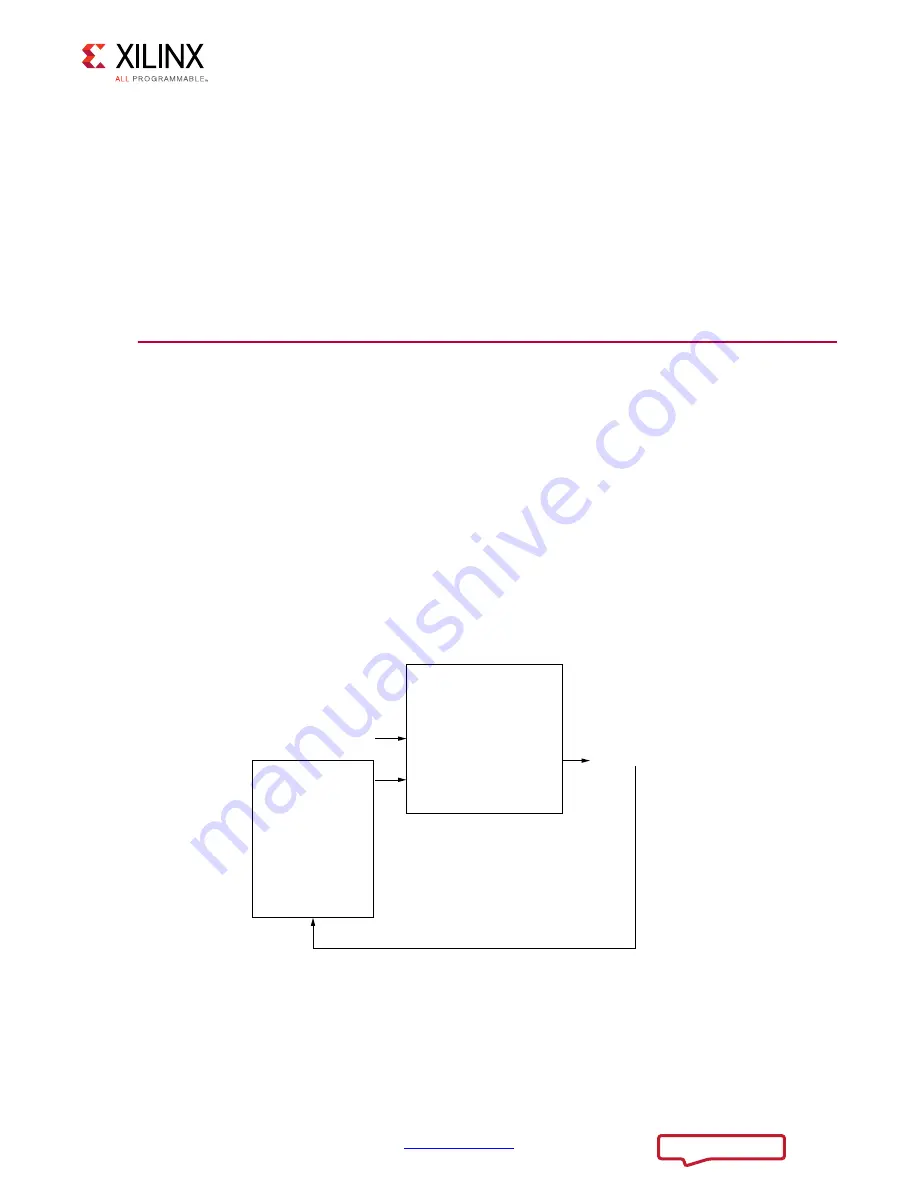

X-Ref Target - Figure 3-2

Figure 3-2:

System Reset Connection

!8)

0#)E

)0

MMCM?LOCK

0%234N

PROC?SYS?RESET

)0

$#-?,/#+%$

!UX?2ESET?)N

)NTERCONNECT?ARESETN

!8)!2%3%4N

AXI?ARESETN

8