AXI Bridge for PCI Express v2.4

4

PG055 June 4, 2014

Product Specification

Introduction

The Xilinx

®

LogiCORE™ IP AXI Root Port/

Endpoint (RP/EP) Bridge for PCI Express® core

is an interface between the AXI4 and PCI

Express. Definitions and references are

provided in this document for all of the

functional modules, registers, and interfaces

that are implemented in the AXI Bridge for PCI

Express core. Definitions are also provided for

the hardware implementation and software

interfaces to the AXI Bridge for PCI Express core

in supported FPGA devices.

Features

•

Zynq®-7000, Kintex®-7, Virtex®-7, and

Artix®-7 FPGA Integrated Blocks for PCI

Express

•

Maximum Payload Size (MPS) up to 256 bytes

•

Multiple Vector Messaged Signaled Interrupts

(MSIs)

•

Legacy interrupt support

•

Memory-mapped AXI4 access to PCIe® space

•

PCIe access to memory-mapped AXI4 space

•

Tracks and manages Transaction Layer Packets

(TLPs) completion processing

•

Detects and indicates error conditions with

interrupts

•

Optimal AXI4 pipeline support for enhanced

performance

•

Compliant with Advanced RISC Machine

(ARM®) Advanced Microcontroller Bus

Architecture 4 (AMBA®) AXI4 specification

•

Supports up to three PCIe 32-bit or 64-bit

PCIe Base Address Registers (BARs) as

Endpoint

•

Supports a single PCIe 32-bit or 64-bit BAR as

Root Port

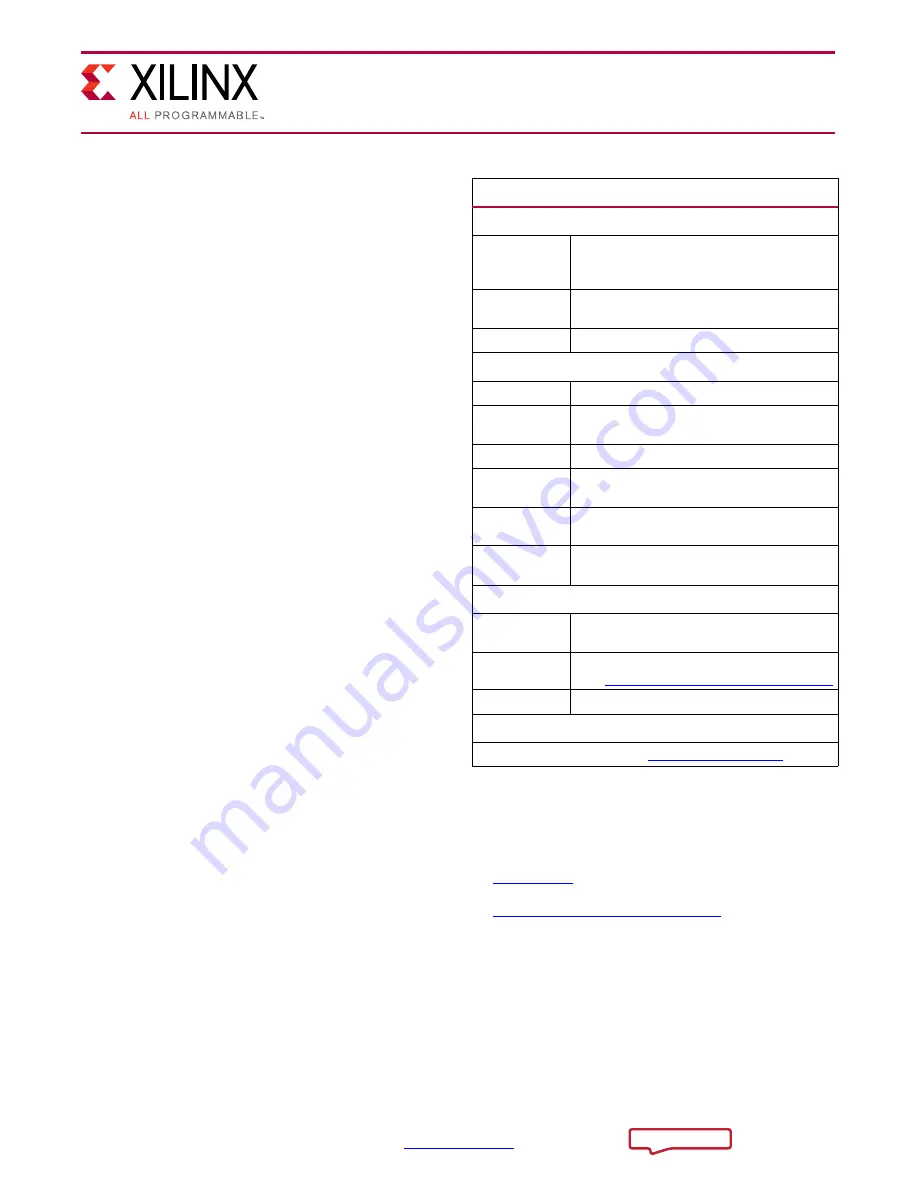

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family

Zynq-7000, 7 Series

Supported

User Interfaces

AXI4

Resources

See

Provided with Core

Design Files

VHDL and Verilog

Example

Design

Verilog

Test Bench

Verilog

Constraints

File

XDC

Simulation

Model

Not Provided

Supported

S/W Driver

Standalone and Linux

Tested Design Flows

Design Entry

Vivado® Design Suite

Vivado IP integrator

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide

Synthesis

Vivado Synthesis

Support

Provided by Xilinx @

Notes:

1. For a complete list of supported devices, see the Vivado IP

catalog. See also

2. Standalone driver details can be found in the SDK directory

(<

install_directory

>/doc/usenglish/xilinx_drivers.htm). Linux

OS and driver support information is available from

.

3. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide

4. Except for XC7VX485T, Virtex 7 devices are not supported.