AXI Bridge for PCI Express v2.4

74

PG055 June 4, 2014

Chapter 4:

Design Flow Steps

AXI Base Address Registers

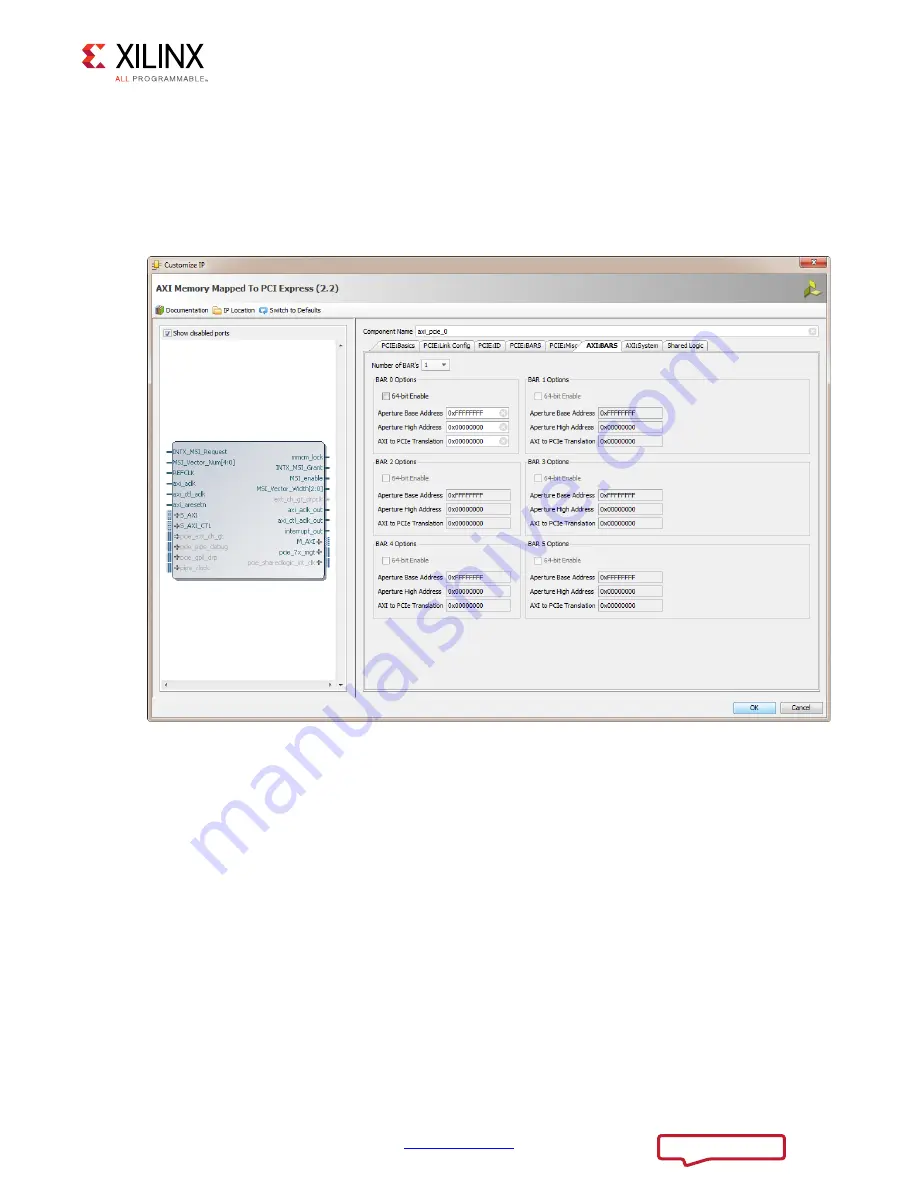

The AXI Base Address Registers (BARs) screen shown in

registers and the translation between AXI Memory space and PCI Express Memory space.

Each BAR has a Base Address, High Address, and translation field which can be configured

through the Vivado IDE.

Number of BARs

Indicates the number of AXI BARs enabled.The BARs are enabled sequentially.

64-bit Enable

Indicates if the AXI Base Address Register is 64-bit addressable. Selecting a 64-bit BAR

consumes the subsequent BAR.

Aperture Base Address

Sets the base address for the address range associated to the BAR. You should edit this

parameter to fit design requirements.

X-Ref Target - Figure 4-6

Figure 4-6:

AXI Base Address Registers