AXI Bridge for PCI Express v2.4

22

PG055 June 4, 2014

Chapter 2:

Product Specification

Parameter Dependencies

lists the parameter dependencies.

G58

NUM_READ_

OUTSTANDING

AXI Interconnect

Slave Port Read

Pipeline Depth

1: Only one active AXI

ARADDR can be accepted

in AXI slave bridge PCIe.

2, 4, 8: Size of pipeline for

active AXI ARADDR values

to be stored in AXI slave

bridge PCIe

A value of 8 is not allowed

for 128-bit core (Gen2 7

series) configurations. The

maximum setting of this

parameter value is 4.

8

Integer

AXI4 Master Interconnect Parameters

G59

NUM_WRITE_

OUTSTANDING

AXI Interconnect

Master Bridge write

address issue depth

1, 2, 4: Number of actively

issued AXI AWADDR

values on the AXI

Interconnect to the target

slave device(s).

4

Integer

G60

NUM_READ_

OUTSTANDING

AXI Interconnect

Master Bridge read

address issue depth

1, 2, 4: Number of actively

issued AXI ARADDR values

on the AXI Interconnect to

the target slave device(s).

4

Integer

Notes:

1. This is a 32-bit address.

2. The width of this should match the address size (C_AXIBAR_AS) for this BAR.

3. The range specified must comprise a complete, contiguous power of two range, such that the range = 2

n

and the

n

least

significant bits of the Base Address are zero. The address value is a 32-bit AXI address.

4. The difference between C_AXIBAR_n and C_AXIBAR_HIGHADDR_n must be less than or equal to 0x7FFF_FFFF and greater

than or equal to 0x0000_1FFF.

5. It is recommended that you do not edit these default values on the AXI bridge for PCIe IP unless you need to reduce the

resource utilization. Doing so impacts the AXI bridge performance.

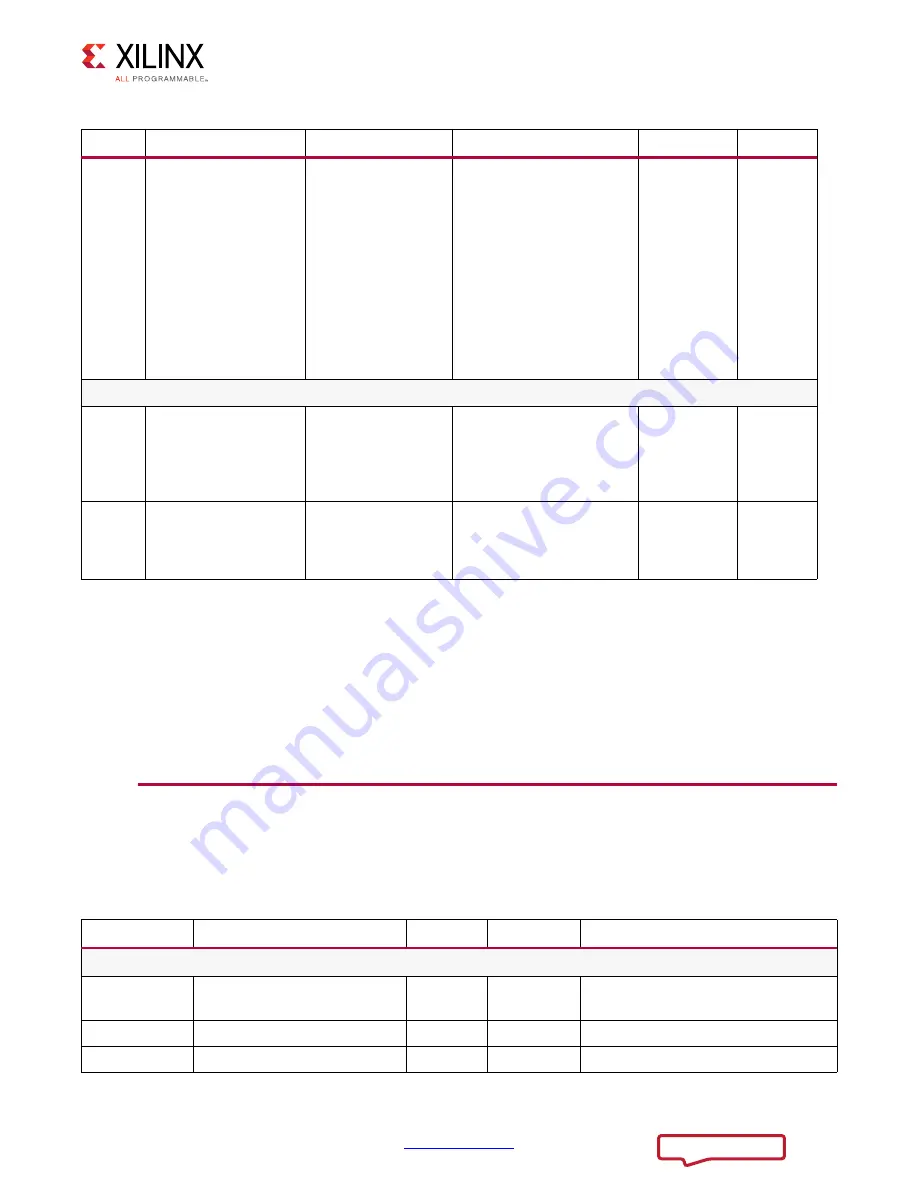

Table 2-4:

Top-Level Parameters

(Cont’d)

Generic

Parameter Name

Description

Allowable Values

Default Value VHDL Type

Table 2-5:

Parameter Dependencies

Generic

Parameter

Affects

Depends

Description

Bridge Parameters

G1

C_FAMILY

,

,

,

G2

C_INCLUDE_RC

Meaningful only if G1 = Kintex-7.

G3

C_COMP_TIMEOUT