AXI Bridge for PCI Express v2.4

29

PG055 June 4, 2014

Chapter 2:

Product Specification

Bridge Status and Control Register (Offset 0x134)

The Bridge Status and Control register (described in

) provides information about

the current state of the AXI4-Stream Bridge. It also provides control over how reads and

writes to the Core Configuration Access aperture are handled.

Interrupt Decode Register (Offset 0x138)

The Interrupt Decode register (described in

) provides a single location where the

host processor interrupt service routine can determine what is causing the interrupt to be

asserted and how to clear the interrupt. Writing a

1'b1

to any bit of the Interrupt Decode

register clears that bit except for the Correctable, Non-Fatal, and Fatal bits.

Follow this sequence to clear the Correctable, Non-Fatal, and Fatal bits:

1. Clear the Root Port Error FIFO (0x154) by performing first a read, followed by write-back

of the same register.

2. Write to the Interrupt Decode Register (0x138) with ‘1’ to the appropriate error bit to

clear it.

IMPORTANT:

An asserted bit in the Interrupt Decode register does not cause the interrupt line to assert

unless the corresponding bit in the Interrupt Mask register is also set.

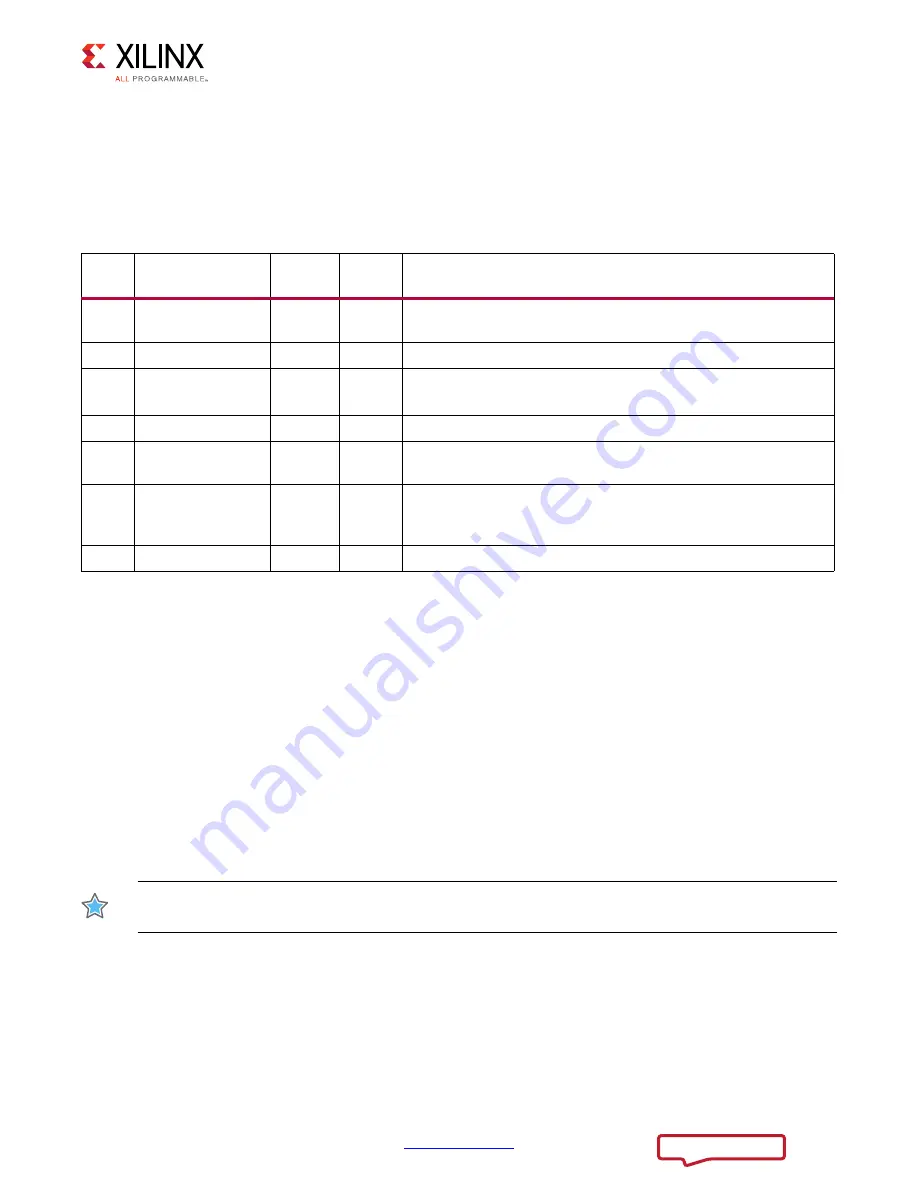

Table 2-11:

Bridge Status and Control Register

Bits

Name

Core

Access

Reset

Value

Description

0

ECAM Busy

RO

0

Indicates an ECAM access is in progress (waiting for

completion).

7:1

Reserved

RO

0

Reserved

8

Global

Disable

RW

0

When set, disables interrupt line from being asserted. Does not

prevent bits in Interrupt Decode register from being set.

15:9

Reserved

RO

0

Reserved

16

RW1C as RW

RW

0

When set, allows writing to core registers which are normally

RW1C.

17

RO as RW

RW

0

When set, allows writing to certain registers which are normally

RO.

(Only supported for Kintex-7 FPGA cores.)

31:18 Reserved

RO

0

Reserved