CAN FD v2.0

22

PG223 December 5, 2018

Chapter 2:

Product Specification

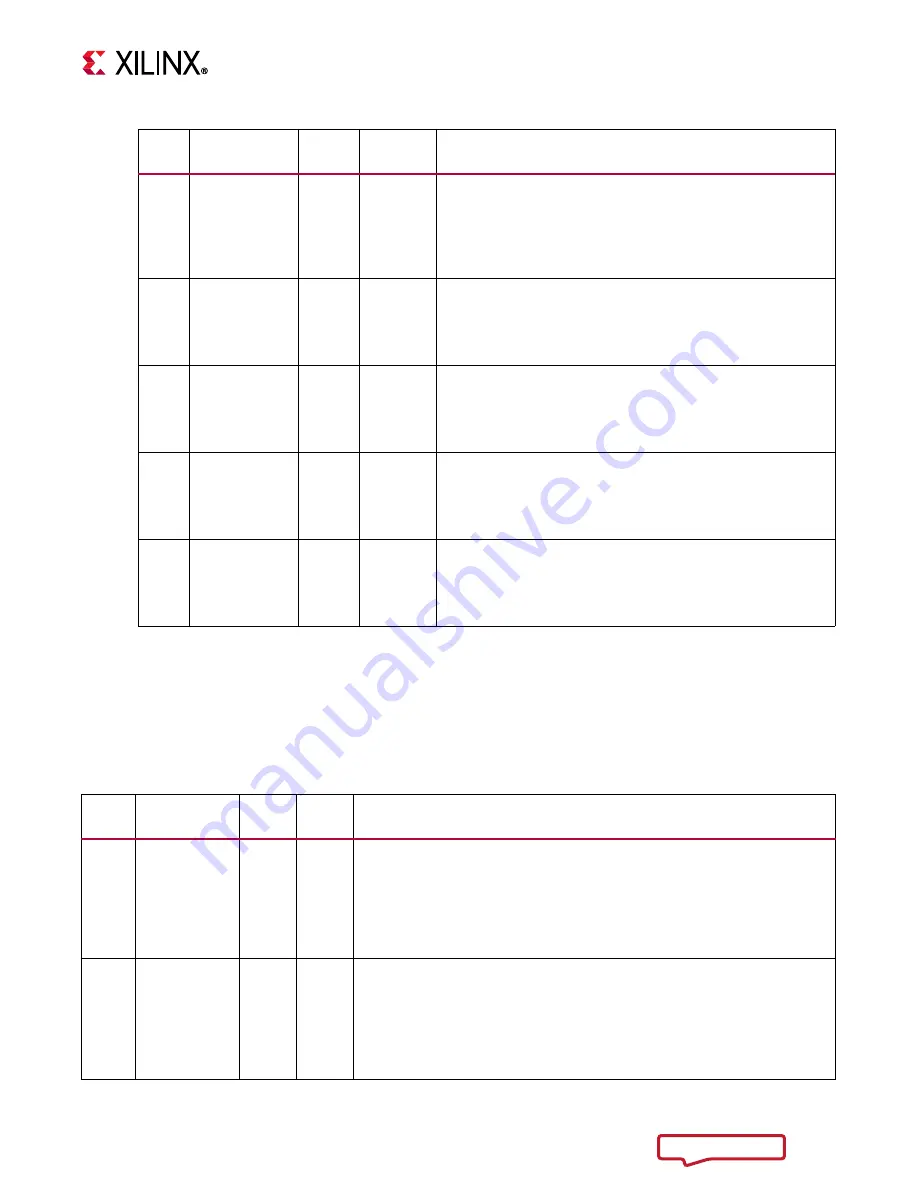

Interrupt Status Register (Address 0x001C)

Interrupt status bits in the ISR can be cleared by writing to the Interrupt Clear register. For

all bits in the ISR, a set condition takes priority over the clear condition and the bit

continues to remain 1.

4

BIDLE

R

0

Bus Idle.

Indicates the CAN bus status.

• 1 = Indicates no bus communication is taking place.

• 0 = Indicates the core is either in Configuration mode or

the bus is busy.

3

NORMAL

R

0

Normal Mode.

Indicates that the core is in Normal mode.

• 1 = Indicates that the core is in Normal mode.

• 0 = Indicates that the core is not in Normal mode.

2

SLEEP

R

0

Sleep Mode.

Indicates that the core is in Sleep mode.

• 1 = Indicates that the core is in Sleep mode.

• 0 = Indicates that the core is not in Sleep mode.

1

LBACK

R

0

Loopback Mode.

Indicates that the core is in Loopback mode.

• 1 = Indicates that the core is in Loopback mode.

• 0 = Indicates that the core is not in Loopback mode.

0

CONFIG

R

1

Configuration Mode Indicator.

Indicates that the core is in Configuration mode.

• 1 = Indicates that the core is in Configuration mode.

• 0 = Indicates that the core is not in Configuration mode.

Table 2-11:

Status Register

(Cont’d)

Bits

Name

Access

Default

Value

Description

Table 2-12:

Interrupt Status Register

Bits

Name

Access Default

Value

Description

31

TXEWMFLL

R

0

TX Event FIFO Watermark Full Interrupt.

• 1 = Indicates that TX Event FIFO is full based on watermark

programming.

The interrupt continues to assert as long as the TX Event FIFO Fill Level

is above TX Event FIFO Full watermark. This bit can be cleared by

writing to the respective bit in the ICR.

30

TXEOFLW

R

0

TX Event FIFO Overflow Interrupt.

• 1 = Indicates that a message has been lost. This condition occurs

when the core has successfully transmitted a message for which an

event store is requested but the TX Event FIFO is full.

This bit can be cleared by writing to the respective bit in the ICR.

This bit is also cleared when a 0 is written to the CEN bit in the SRR.