CAN FD v2.0

65

PG223 December 5, 2018

Chapter 3:

Designing with the Core

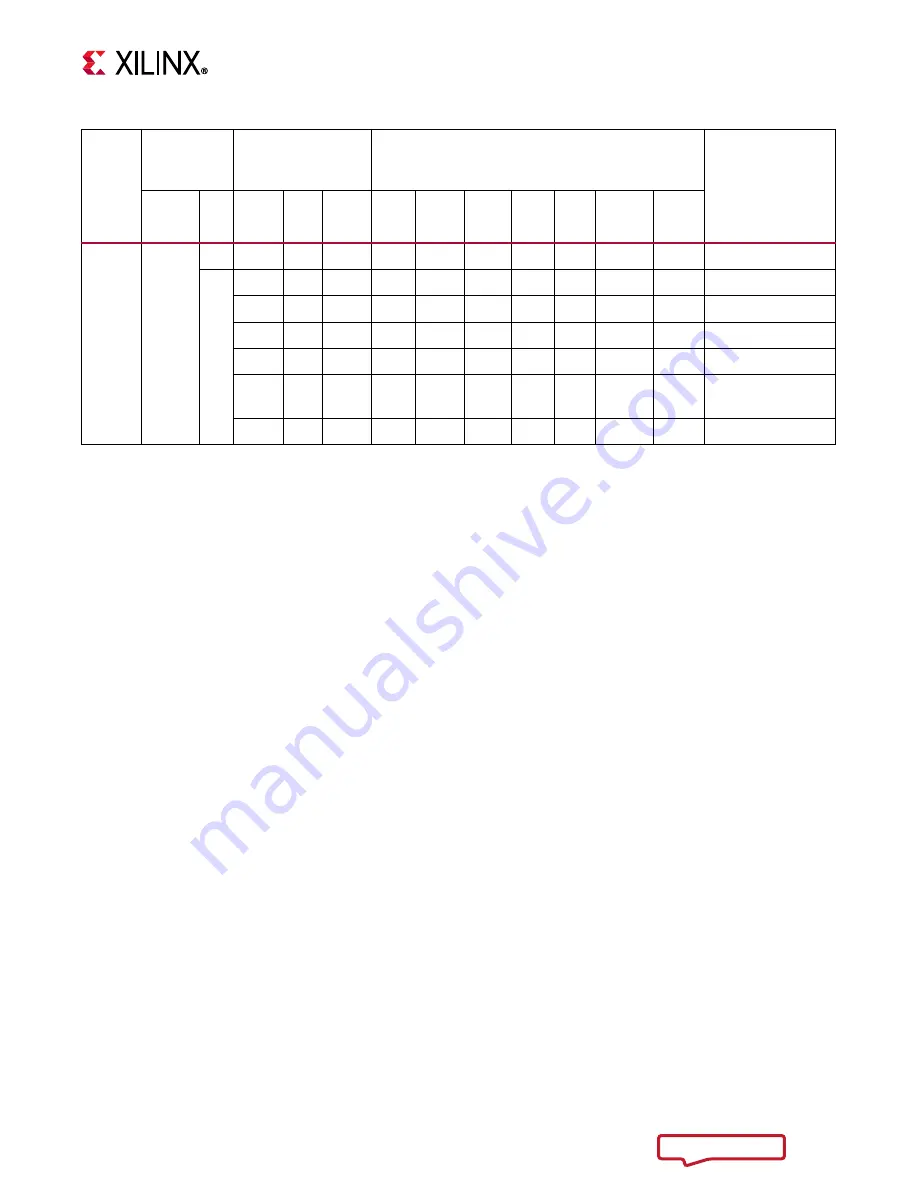

Configuration Mode

The core enters Configuration mode, irrespective of the operation mode, when any of the

following actions are performed:

• Writing a 0 to the

CEN

bit in the SRR register.

• Writing a 1 to the

SRST

bit in the SRR register.

• Driving a 0 on the Reset input.

After reset, the core exits Configuration mode after the

CEN

bit is set and 11 consecutive

nominal recessive bits are seen on the CAN bus.

1

0

0

X

X

X

1

0

0

0

0

0

0

Configuration

1

0

0

0

0

0

0

0

0

1

0

Normal

0

0

1

0

0

0

0

0

1

1

Snoop

0

1

0

0

0

0

0

1

0

0

Sleep

1

0

0

0

0

0

1

0

0

0

Loopback

0

X

0

0

1

0

0

0

X

0

Bus-Off

Recovery

0

X

X

0

0

1

0

0

X

X

PEE

Notes:

1. X-Control bit don’t care. Status bit does not mean anything.

2. Transition to Bus-Off state depends on Transmit Error Count value as per standard specification. Recovery from Bus-Off state

depends on SBR and ABR bit settings in the MSR register (as per respective bit behavior description). Bus-Off Recovery can

be tracked through status bit BSFR_CONFIG in SR register and REC field in ECR register. Entry and exit from Bus-Off state can

also generate interrupt.

3. Transition to CAN FD Protocol Exception State (PEE) depends on the DPEE bit in MSR register. The core enters and exits PEE

state as per ISO standard specification and this is reflected by status bit PEE_CONFIG in the SR register. Entry to PEE state

can also generate interrupt.

Table 3-1:

CAN FD Core Operating Mode Transitions

(Cont’d)

System

(Hard)

Reset

SRR

Register

Bits

MSR Register Bits

SR (Status) Register Bits

Operation Mode

SRST

(SW

Reset)

CEN LBACK SLEEP SNOOP Config

BSFR_

Config

PEE_

Config

LBACK SLEEP NORMAL SNOOP