Page 279

TMP89FM42

RA001

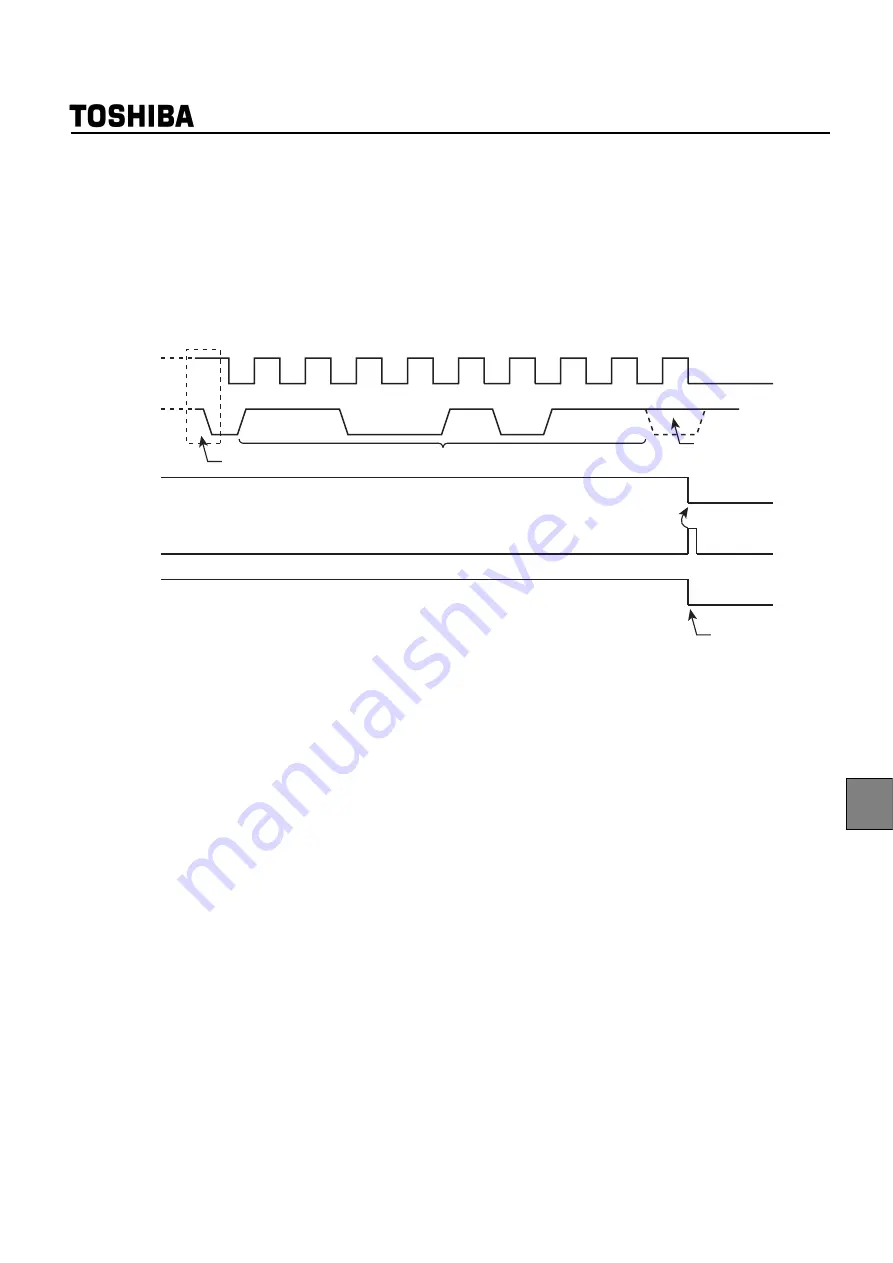

Figure 18-17 Generating the Start Condition and the Slave Address

18.5.3 1-word data transfer

Check SBI0SR2<MST> by the interrupt process after a 1-word data transfer is completed, and determine

whether the mode is a master or slave.

18.5.3.1 When SBI0SR2<MST> is "1" (Master mode)

Check SBI0SR2<TRX> and determine whether the mode is a transmitter or receiver.

(1)

When SBI0SR2<TRX> is "1" (Transmitter mode)

Check SBI0SR2<LRB>. When SBI0SR2<LRB> is "1", a receiver does not request data. Imple-

ment the process to generate a stop condition (described later) and terminate data transfer.

When SBI0SR2<LRB> is "0", the receiver requests subsequent data. When the data to be transmit-

ted subsequently is other than 8 bits, set SBI0CR1<BC> again, set SBI0CR1<ACK> to "1", and

write the transmitted data to SBI0DBR.

After writing the data, SBI0CR2<PIN> becomes "1", a serial clock pulse is generated for transfer-

ring the subsequent 1-word data from the SCL0 pin, and then the 1-word data is transmitted from the

SDA0 pin.

After the data is transmitted, an interrupt request occurs. SBI0CR2<PIN> become "0" and the

SCL0 pin is set to the low level. If the data to be transferred is more than one word in length, repeat

the procedure from the SBI0SR2<LRB> checking above.

Example :Generate the start condition

CHK_BB:

TEST

(SBI0SR2).BB

; Confirms that the bus is free

JR

F, CHK_BB

LD

(SBI0DBR), 0xcb

; The transmission slave address 0x65 and the direction bit "1"

LD

(SBI0CR2), 0xf8

; Write "1" to SBI0CR2<MST>, <TRX>, <BB> and <PIN> to "1"

Start condition

Slave a Direction bit

2

3

4

5

6

7

8

9

1

Acknowledgem

ent signal from

a slave

Interrupt request

signal

SBI0CR1<PIN>

SCL0 pin

SDA0 pin

SBI0CR2 <TRX> is cleared to "0" when

the direction bit is "1"and an

acknowledge signal is returned.

SBI0CR2<TRX>

Summary of Contents for TLCS-870/C1 Series

Page 1: ...8 Bit Microcontroller TLCS 870 C1 Series TMP89FM42 查询TMP89FM42供应商 捷多邦 专业PCB打样工厂 24小时加急出货 ...

Page 3: ...Revision History Date Revision 2007 10 25 1 First Release 2007 11 3 2 Contents Revised ...

Page 4: ......

Page 14: ......

Page 18: ...1 3 Block Diagram TMP89FM42 1 3 Block Diagram Figure 1 2 Block Diagram ...

Page 22: ...1 4 Pin Names and Functions TMP89FM42 ...

Page 60: ...2 CPU Core 2 5 Revision History TMP89FM42 ...

Page 76: ...3 Interrupt Control Circuit 3 8 Revision History TMP89FM42 ...

Page 86: ...4 External Interrupt control circuit 4 3 Function TMP89FM42 ...

Page 102: ...7 Voltage Detection Circuit 7 5 Revision History TMP89FM42 ...

Page 126: ...8 I O Ports 8 3 I O Port Registers TMP89FM42 Note 2 i 0 to 1 ...

Page 136: ...8 I O Ports 8 5 Revision History TMP89FM42 ...

Page 142: ...9 Special Function Registers 9 3 SFR3 0x0E40 to 0x0EFF TMP89FM42 ...

Page 146: ...10 Low Power Consumption Function for Peripherals TMP89FM42 ...

Page 149: ...TMP89FM42 11 3 Revision History Rev Description RA001 Deleted SLEEP2 description ...

Page 150: ...11 Divider Output DVO 11 3 Revision History TMP89FM42 ...

Page 220: ...15 Real Time Clock RTC 15 4 Real Time Clock Operation TMP89FM42 ...

Page 250: ...16 Asynchronous Serial Interface UART 16 15 Revision History TMP89FM42 ...

Page 302: ...18 Serial Bus Interface SBI 18 7 Revision History TMP89FM42 ...

Page 338: ...21 Flash Memory 21 4 Toggle Bit D6 TMP89FM42 ...

Page 384: ...22 Serial PROM Mode 22 15 Revision History TMP89FM42 ...

Page 388: ...24 Input Output Circuit 24 1 Control Pins TMP89FM42 ...

Page 404: ...25 Electrical Characteristics 25 11 Revision History TMP89FM42 ...

Page 406: ...26 Package Dimensions TMP89FM42 ...

Page 408: ......