Page 308

21. Flash Memory

TMP89FM42

RA003

21.2.2 Flash memory area switching (FLSCR1<FAREA>)

To perform an erase or write on the flash memory, a memory transfer instruction (command sequence) must

be executed. If a memory transfer instruction is used to read or write data, a read or write can be performed

only on the data area. To perform an erase or write on the code area, therefore, part of the code area must be

temporarily switched to the data area. This switching between data and code areas is performed by making the

appropriate FLSCR1<FAREA> setting.

By setting "0xD5" on FLSCR2<CR1EN> after setting FLSCR1<FAREA> to "10", 0x8000 through 0xFFFF

(AREA C1) in the code area is mapped to 0x8000 through 0xFFFF (AREA D1) in the data area.

To restore the flash memory to the initial state of mapping, set FLSCR1<FAREA> to "00", and then set

"0xD5" on FLSCR2<CR1EN>.

All flash memory areas can be accessed by performing the appropriate steps described above and then exe-

cuting the memory transfer instruction on 0x8000 through 0xFFFF (AREA D1) in the data area.

Additionally, access to areas to which memory is not assigned should be avoided by executing an instruction

or specifying such an area by using jump or call instructions.

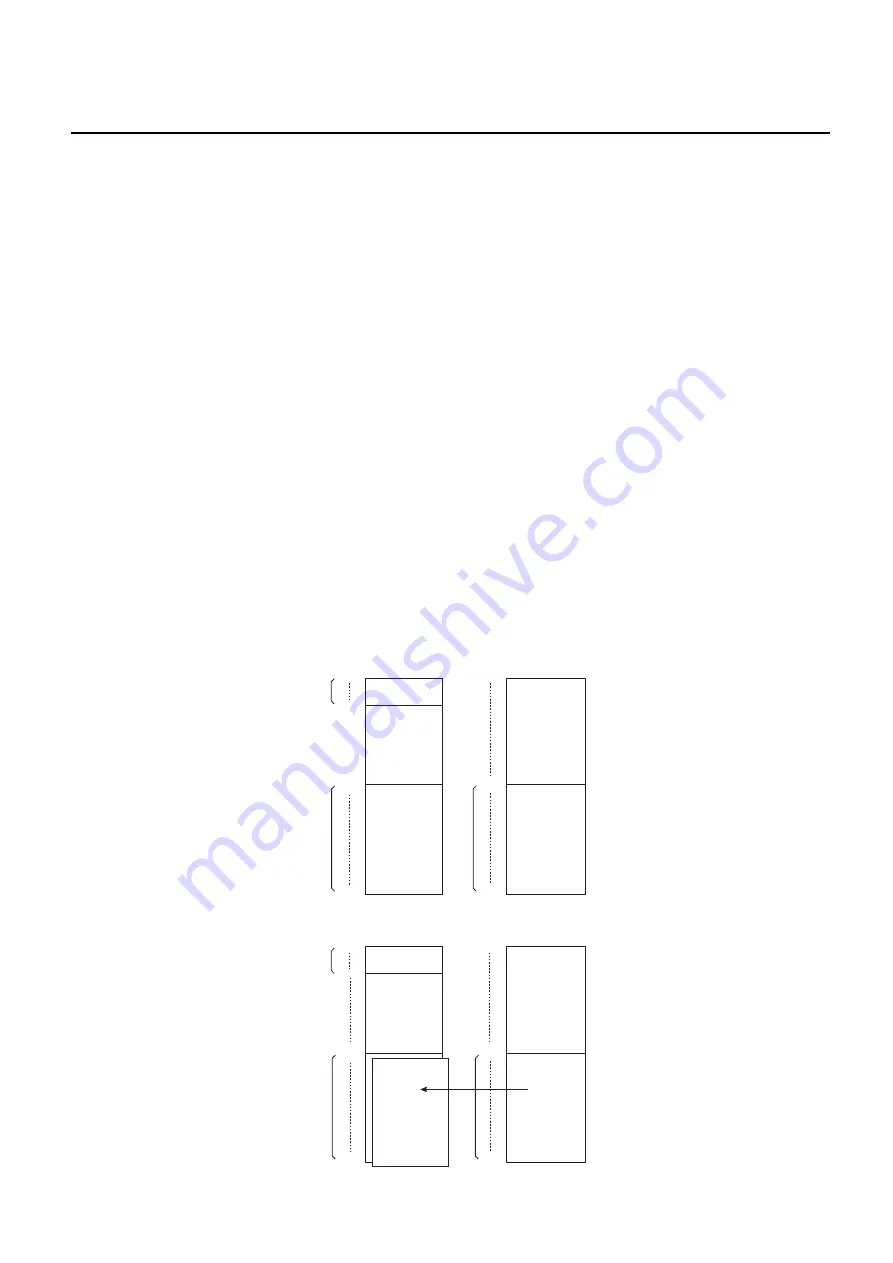

Figure 21-1 Area Switching Using the FLSCR1<FAREA> Setting

0x8000 through 0xFFFF (AREA D1) in the data area and 0x8000 through 0xFFFF (AREA C1) in the code

area are mirror areas; these two areas refer to the same physical address in memory. Therefore, an erase or write

must be performed on one of these two mirror areas. For example, If a write is performed on 0x8000 in the data

area with FLSCR1<FAREA> set to "10" after performing a write on 0x8000 in the data area with

FLSCR1<FAREA> set to "00", data is overwritten. To write data to the flash memory that already has data writ-

ten to it, existing data must first be erased from the flash memory by performing a sector erase or chip erase, and

then data must be written.

0xFFFF

0xFFFF

0x8000

0x7FFF

0x8000

0x7FFF

Data area

If FLSCR<FAREA> = “00”

Code area

0x0000

0x0000

SFR

RAM

0x0FFF

Flash

Flash

0x0000

SFR

RAM

0x0FFF

0x8000

0x7FFF

32768

bytes

32768

bytes

AREA C1

AREA D1

If FLSCR<FAREA> = “10”

Flash

Flash

0xFFFF

0x0000

0xFFFF

0x8000

0x7FFF

Data area

Code area

32768

bytes

AREA C1

AREA C1

32768

bytes

Summary of Contents for TLCS-870/C1 Series

Page 1: ...8 Bit Microcontroller TLCS 870 C1 Series TMP89FM42 查询TMP89FM42供应商 捷多邦 专业PCB打样工厂 24小时加急出货 ...

Page 3: ...Revision History Date Revision 2007 10 25 1 First Release 2007 11 3 2 Contents Revised ...

Page 4: ......

Page 14: ......

Page 18: ...1 3 Block Diagram TMP89FM42 1 3 Block Diagram Figure 1 2 Block Diagram ...

Page 22: ...1 4 Pin Names and Functions TMP89FM42 ...

Page 60: ...2 CPU Core 2 5 Revision History TMP89FM42 ...

Page 76: ...3 Interrupt Control Circuit 3 8 Revision History TMP89FM42 ...

Page 86: ...4 External Interrupt control circuit 4 3 Function TMP89FM42 ...

Page 102: ...7 Voltage Detection Circuit 7 5 Revision History TMP89FM42 ...

Page 126: ...8 I O Ports 8 3 I O Port Registers TMP89FM42 Note 2 i 0 to 1 ...

Page 136: ...8 I O Ports 8 5 Revision History TMP89FM42 ...

Page 142: ...9 Special Function Registers 9 3 SFR3 0x0E40 to 0x0EFF TMP89FM42 ...

Page 146: ...10 Low Power Consumption Function for Peripherals TMP89FM42 ...

Page 149: ...TMP89FM42 11 3 Revision History Rev Description RA001 Deleted SLEEP2 description ...

Page 150: ...11 Divider Output DVO 11 3 Revision History TMP89FM42 ...

Page 220: ...15 Real Time Clock RTC 15 4 Real Time Clock Operation TMP89FM42 ...

Page 250: ...16 Asynchronous Serial Interface UART 16 15 Revision History TMP89FM42 ...

Page 302: ...18 Serial Bus Interface SBI 18 7 Revision History TMP89FM42 ...

Page 338: ...21 Flash Memory 21 4 Toggle Bit D6 TMP89FM42 ...

Page 384: ...22 Serial PROM Mode 22 15 Revision History TMP89FM42 ...

Page 388: ...24 Input Output Circuit 24 1 Control Pins TMP89FM42 ...

Page 404: ...25 Electrical Characteristics 25 11 Revision History TMP89FM42 ...

Page 406: ...26 Package Dimensions TMP89FM42 ...

Page 408: ......