172

Data Streaming and Capture

Appendix D

SR865A DSP Lock-in Amplifier

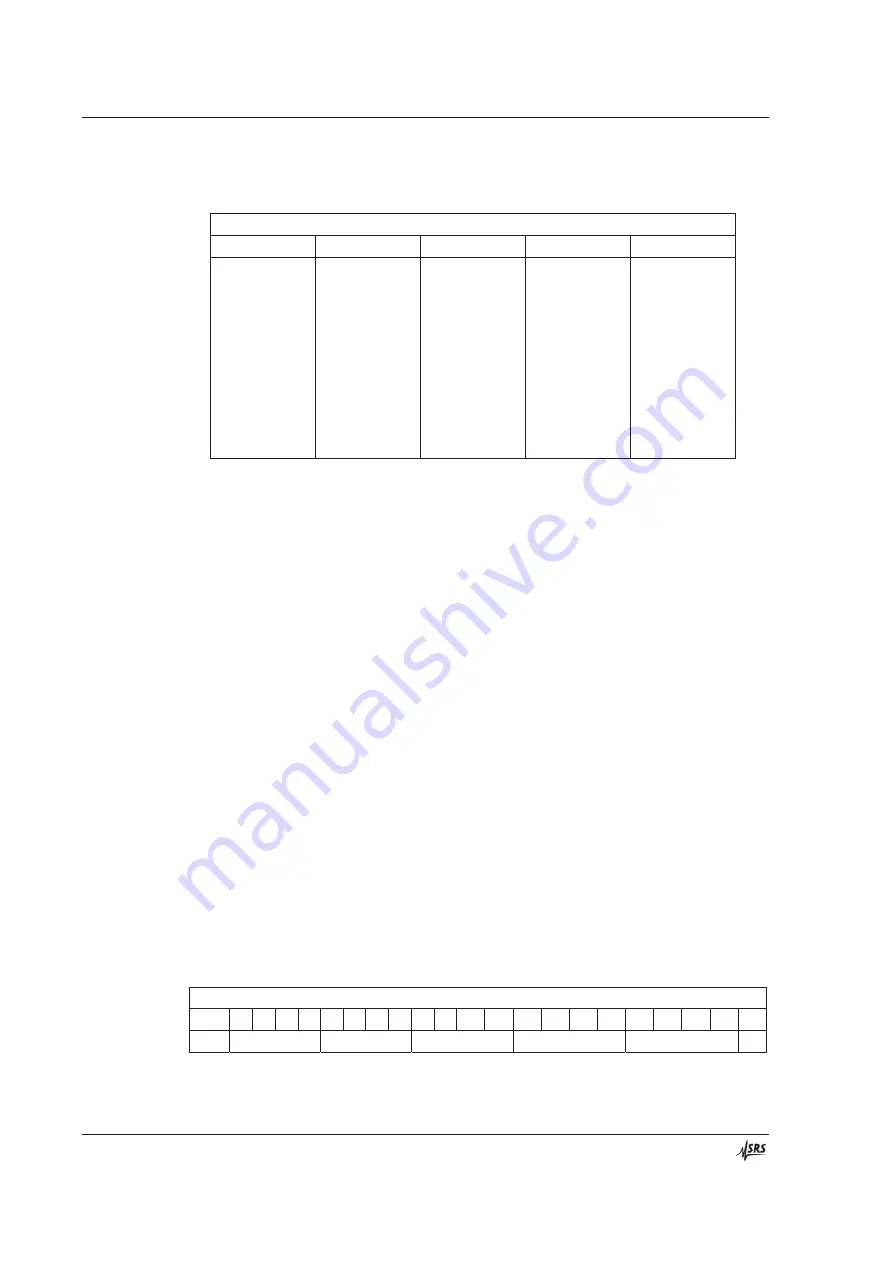

The header word consists of the following fields:

Header bits

31

–

24 (MSB)

23

–

16 15

–

12 11

–

8 7

–

0 (LSB)

Status

Bit 24: Overload

Bit 25: Error

Bit 28: Little-end

Bit 29:Checksum

Sample rate

0: 1.25 MHz

1: 625 kHz

2: 312.5 kHz

…

N: 1.25MHz/2

N

,

…

31: 0.582 mHz

Packet length

0: 1024 bytes

1: 512 bytes

2: 256 bytes

3: 128 bytes

Packet content

32 bit floats:

0: X

1: XY

2: Rθ

3: XYRθ

16 bit integers:

4: X

5: XY

6: Rθ

7: XYRθ

Packet counter

0

–

255

Packet counter:

allows the receiving computer to detect lost or dropped packets. Each

UDP packet has a packet count that is one greater than the previous packet, modulo 256.

Packet content:

indicates the data contained in the packet.

Packet length

: the number of bytes of data that follow.

Sample rate:

is the sample rate of the data in the packet. A value of N corresponds to a

sampling rate of 1.25 MHz/(2

N

), where N is a value between 0 and 31 inclusive. This

sample rate already takes into account the subsampling requested in the command

STREAMRATE.

Status:

bit 24 is high when an input overload, sync filter overload (if sync filter is on), or

output overload (if integer data is contained in the packet) condition existed at the

beginning of the packet. Bit 25 is high when a PLL unlock or sync filter out-of-range

condition existed at the beginning of the packet.

Bit 28 is high if data is stored in little-endian format, and low if it is in big-endian format.

Bit 29 indicates that integrity-checking (UDP packet checksumming) is enabled.

After reading the header information, it is possible to correctly interpret the data in the

rest of the packet. If you need to do endian-conversion, floating-point data must be

converted 32 bits (4 bytes) at a time, whereas integer data must be converted 16 bits (2

bytes) at a time.

XYR

θ

data is recorded in that order, followed by the next sample of XYR

θ

. As an

example, let's say the packet contains floating-point XYR

θ

data:

Data bytes

Byte

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

…

Data

X(0) Y(0) R(0)

θ

(0)

X(1)

…

Summary of Contents for SR865A

Page 5: ...Safety and Preparation For Use iii SR865A DSP Lock in Amplifier...

Page 6: ...iv Safety and Preparation For Use SR865A DSP Lock in Amplifier...

Page 54: ...36 Getting Started Chapter 1 SR865A DSP Lock in Amplifier...

Page 118: ......

Page 172: ......

Page 186: ...168 The FFT Display Appendix B SR865A DSP Lock in Amplifier...

Page 192: ......