PDP-503CMX, PDP-503MXE, PDA-5002

173

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

QO1

QO0

HSYNC

DE

ODCK

OVDD

CTL3

CTL2

CTL1

GND

DVDD

QE23

QE22

QE20

QE19

QE17

QE16

OVDD

OGND

QE15

QE14

OGND

OVDD

AGND

Rx2+

Rx2

±

AVDD

AGND

AVDD

Rx1

±

AGND

AGND

Rx0+

Rx0

±

AGND

RxC+

RxC

±

AVDD

EXT_RES

PGND

RSVD

OCK_INV

QO22

QO21

QO20

QO18

QO17

QO16

GND

DVDD

QO13

QO12

QO9

QO8

OGND

OVDD

QO7

QO6

QO5

QO4

QO3

QO2

DFO

PD

ST

PIXS

GND

DVDD

ST

AG

PDO

QE0

QE2

QE3

QE4

QE5

QE6

OVDD

OGND

QE9

QE1

1

QE12

QE13

QE7

QO23

AVDD

QO1

1

QO15

QO14

OGND

QE18

SCDT

QE8

QE1

QE10

QE21

VSYNC

QO10

QO19

Rx1+

PVDD

_

+

Latch

Channel 2

_

+

Latch

Channel 1

_

+

Latch

Channel 0

_

+

PLL

Data Recovery

and

Synchronization

TMDS

Decoder

CH2(0-9)

CH1(0-9)

CH0(0-9)

Panel

Interface

RED(0-7)

CTL3

CTL2

GRN(0-7)

CTL1

BLU(0-7)

VSYNC

HSYNC

QE(0-23)

QO(0-23)

ODCK

DE

SCDT

CTL3

CTL2

CTL1

VSYNC

HSYNC

1.8 V

Regulator

3.3 V

Internal 50-

Ω

Termination

3.3 V

3.3 V

Rx2+

Rx2-

Rx1+

Rx1-

Rx0+

Rx0-

RxC+

RxC-

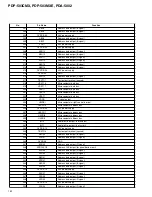

•

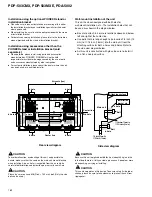

Pin Assignment (Top View)

TFP201A (VIDEO SLOT ST1 ASSY : IC7401)

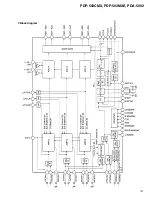

• Panel Bus Receiver

•

Block Diagram

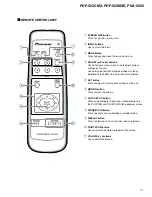

Summary of Contents for PDA-5002

Page 5: ...5 PDP 503CMX PDP 503MXE PDA 5002 ...

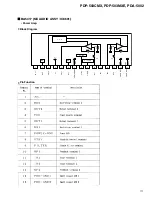

Page 143: ...PDP 503CMX PDP 503MXE PDA 5002 143 Block Diagram Pin Function ...

Page 166: ...PDP 503CMX PDP 503MXE PDA 5002 166 Pin Assignment Top View CXA3516R RGB ASSY IC4603 AD PLL IC ...

Page 167: ...PDP 503CMX PDP 503MXE PDA 5002 167 Block Diagram ...

Page 168: ...PDP 503CMX PDP 503MXE PDA 5002 168 Pin Function ...

Page 169: ...PDP 503CMX PDP 503MXE PDA 5002 169 ...