MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

54

Figure 37 •

AXI INCR16 Write Transaction

Figure 38 •

DDR Controller Command Sequence for AXI INCR16 Write Transaction

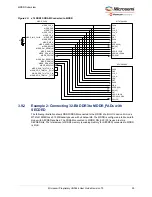

Figure 39 •

AXI INCR-16 Read Transaction and Corresponding DDR Controller Commands

0

0

2 3 4

1

6 7 8

5

10 11 12

9

14 15 16

13

18 19 20

17

22 23 24

21

26 27 28

25

30 31 32

29

34

33

0

0

0

0

f

0

3

1

ff

1 2

3

4

5 6

7

8

9

10

11

12

13 14

15

16

0

CLK

AWADDR

AWID

AWLEN

AWSIZE

AWLOCK

AWBURST

AWVALID

AWREADY

WID

BID

WLAST

WSTRB

WVALID

WDATA

WREADY

BREADY

BVALID

RESP

DDR write controls

0000

0

0008

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0010

0018

0020

0028

0038

0030

MDDR_CLK

MDDR_CLK_N

MDDR_CS_N

MDDR_ODT

MDDR_CKE

MDDR_CAS_N

MDDR_RAS_N

MDDR_RESET_N

MDDR_WE_N

MDDR_ADDR

MDDR_BA

MDDR_DM_RDQS

MDDR_DQS

MDDR_DQS_N

MDDR_DQ

MDDR_DQS_TMATCH_0_IN

MDDR_DQS_TMATCH_0_OUT

mddr_dqs_tmatch_0_out

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

2

3

4

1

7

8

5

6

10

11

12

9

14

15

16

13

18

19

20

17

22

23

24

21

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

0

1

0

0

1

0

0

3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0000

00000000

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

f

00000000

0008

0010

0018

0020

0028

0030

0038

MDDR_CLK

MDDR_CLK_N

MDDR_CS_N

MDDR_ODT

MDDR_CKE

MDDR_CAS_N

MDDR_RAS_N

MDDR_RESET_N

MDDR_WE_N

MDDR_ADDR

MDDR_BA

MDDR_DM_RDQS

MDDR_DQS

MDDR_DQS_N

MDDR_DQ

MDDR_DQS_TMATCH_0_IN

MDDR_DQS_TMATCH_0_OUT

mddr_dqs_tmatch_0_out

CLK

ARADDR

ARID

ARLEN

ARSIZE

ARLOCK

ARBURST

ARVALID

ARREADY

RID

RLAST

RVALID

RDATA

RREADY

CLK_CNT

RESP

DDR write controls

CLK Cycles for compleng

transacon

Read transacon to

DDR Memory iniated

0

Refer

Figure

1-36