Organization of the Board

MEN Mikro Elektronik GmbH

117

20A014-00 E2 – 2007-08-16

5.4

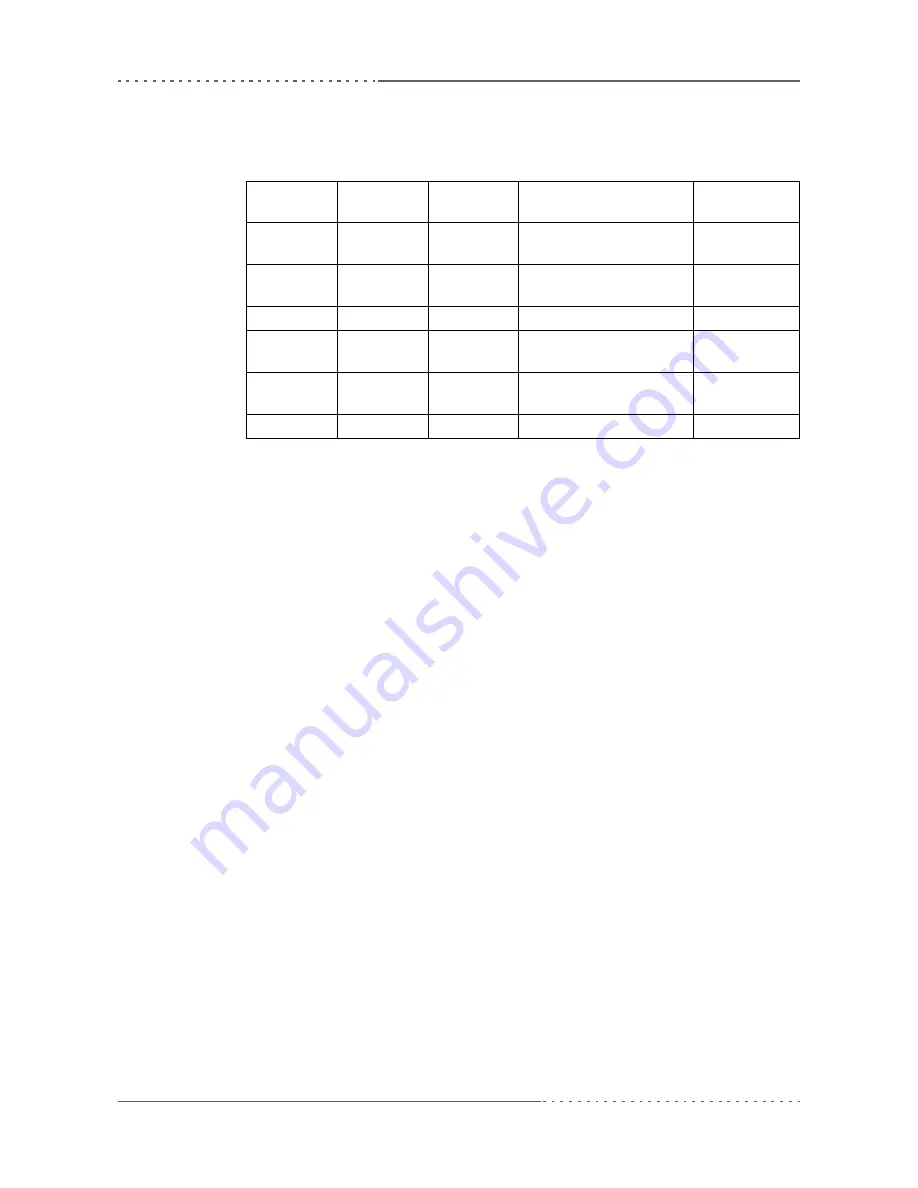

PCI Devices on Bus 0

Table 60.

PCI devices on Bus 0

Device

Number

Vendor ID

Device ID

Function

Interrupt

0x00

0x1057

0x0008

PCI host bridge in

MPC8540

-

0x14

0x3388

0x0026

PCI-to-PCI bridge

INTA, INTB,

INTC, INTD

0x15

0x1172

0x5056

PCI-to-VMEbus bridge

INTB

0x16

0x1415

0x9501

Quad UART COM20..23

(function no. 0)

INTC

0x16

0x1415

0x9511

Quad UART COM20..23

(function no. 1)

INTD

0x1D

0x1172

0x4D45

FPGA

-