Thermal/Mechanical Specifications and Design Guide

105

Quality and Reliability Requirements

9

Quality and Reliability

Requirements

9.1

Use Conditions

Intel evaluates reliability performance based on the use conditions (operating

environment) of the end product by using acceleration models.

The use condition environment definitions provided in

and

based on speculative use condition assumptions, and are provided as

examples only

.

Based on the system enabling boundary condition, the solder ball temperature can vary

and needs to be comprehended for reliability assessment.

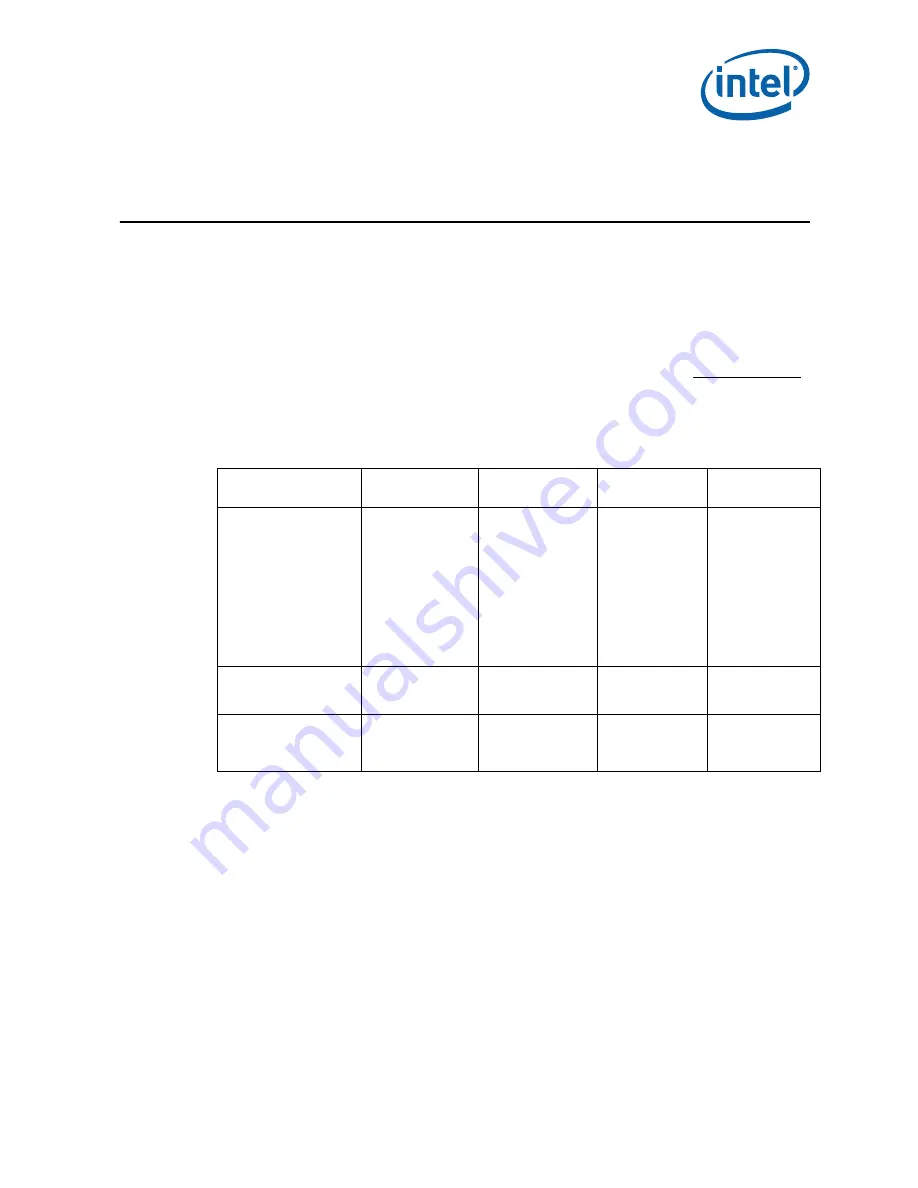

Table 9-1.

Use Conditions Environment (System Level)

Use Environment

Speculative

Stress Condition

Example Use

Condition

Example 7-Yr

Stress Equiv.

Example 10-Yr

Stress Equiv.

Slow small internal

gradient changes due to

external ambient

(temperature cycle or

externally heated)

Fast, large gradient

on/off to max operating

temp.

(power cycle or

internally heated

including power save

features)

Temperature Cycle

DT = 35–44 °C

(solder joint)

550–930 cycles

Temp Cycle

(-25 °C to 100 °C)

780–1345 cycles

Temp Cycle

(-25 °C to 100 °C)

High ambient moisture

during low-power state

(operating voltage)

THB/HAST

T = 25–30 °C

85%RH

(ambient)

110–220 hrs at

110 °C 85%RH

145–240 hrs at

110 °C 85%RH

High Operating

temperature and short

duration high

temperature exposures

Bake

T = 95–105 °C

(contact)

700–2500 hrs at

125 °C

800–3300 hrs at

125 °C

Summary of Contents for BX80619I73820

Page 10: ...10 Thermal Mechanical Specifications and Design Guide...

Page 14: ...Introduction 14 Thermal Mechanical Specifications and Design Guide...

Page 104: ...Thermal Solutions 104 Thermal Mechanical Specifications and Design Guide...

Page 112: ...Mechanical Drawings 112 Thermal Mechanical Specifications and Design Guide...

Page 118: ...Socket Mechanical Drawings 118 Thermal Mechanical Specifications and Design Guide...

Page 124: ...Package Mechanical Drawings 124 Thermal Mechanical Specifications and Design Guide...