Motherboard Layout and Routing Guidelines

2-34

Intel

®

440GX AGPset Design Guide

2.9.6.5

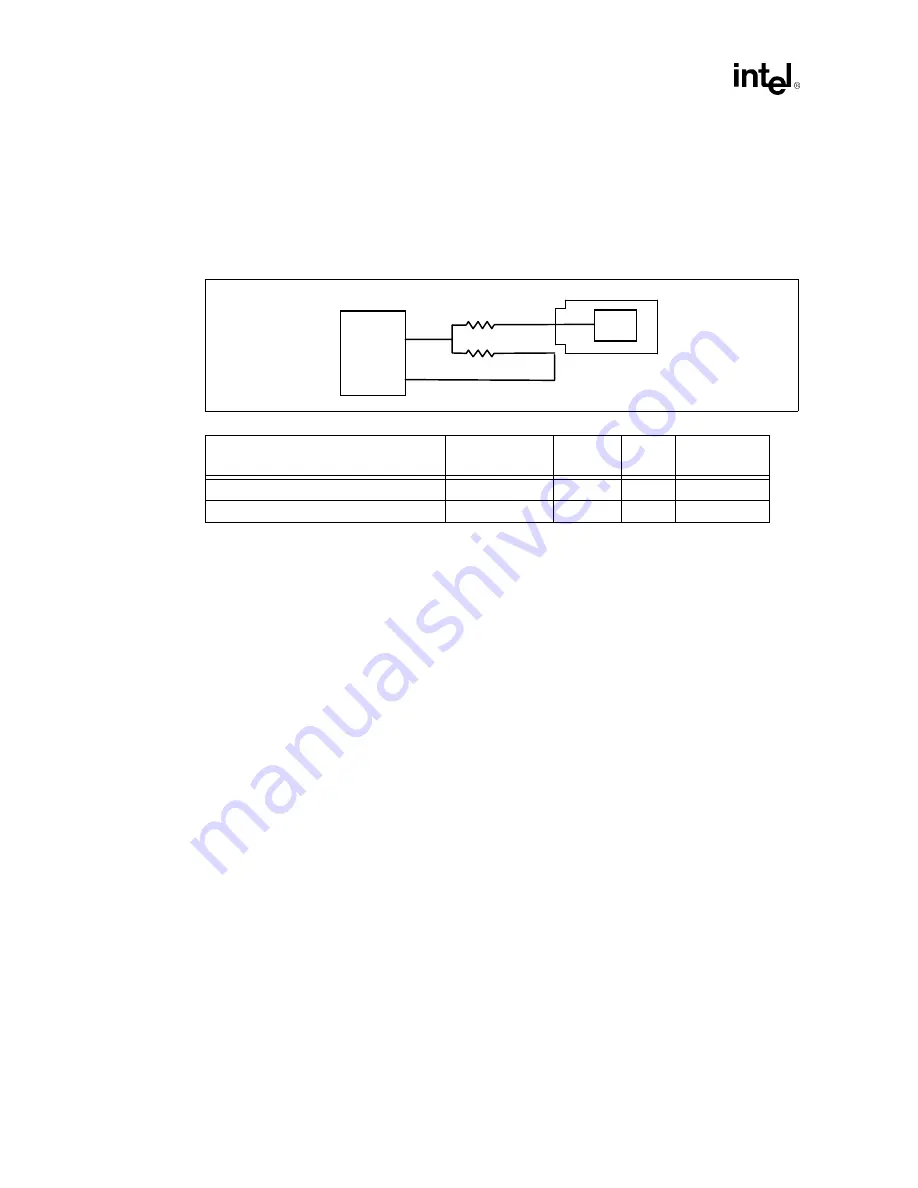

AGP Clock Layout

Series Termination: 22 Ohm series termination should be used for the AGP clocks.

Layout guidelines: The feedback clock trace length equals the standard clock motherboard trace

length plus the card trace length.

Note:

One driver. The signal splits at the 82443GX, each half of the trace goes through a 22 Ohm resistor,

and then to their respective loads. If the graphics chip is down on the motherboard, the trace length

to the graphics chip and the feedback trace length to the 82443GX will both be the same length.

Figure 2-31. AGP Clock Layout

Net

Trace Length

Min

Max

Card Trace

Length

22 Ohm resistor - AGP connector

A

0.5”

12”

~3.3”

22 Ohm resistor - 82443GX (feedback)

A + 3.3”

0.5”

15.3”

NA

GCLKOUT

GCLKIN

AGPCLK

BX

22ohm

22ohm

Summary of Contents for 440GX

Page 1: ...Intel 440GX AGPset Design Guide March 1999 Order Number 290651 001...

Page 10: ...x Intel 440GX AGPset Design Guide...

Page 11: ...1 Introduction...

Page 12: ......

Page 22: ...Introduction 1 10 Intel 440GX AGPset Design Guide...

Page 23: ...2 Motherboard Design...

Page 24: ......

Page 59: ...3 Design Checklist...

Page 60: ......

Page 99: ...4 Debug Recommendations...

Page 100: ......

Page 107: ...5 Third Party Vendors...

Page 108: ......

Page 113: ...A Reference Design Schematics...

Page 114: ......