XC886/888CLM

Controller Area Network (MultiCAN) Controller

User’s Manual

15-74

V1.3, 2010-02

MultiCAN, V1.0

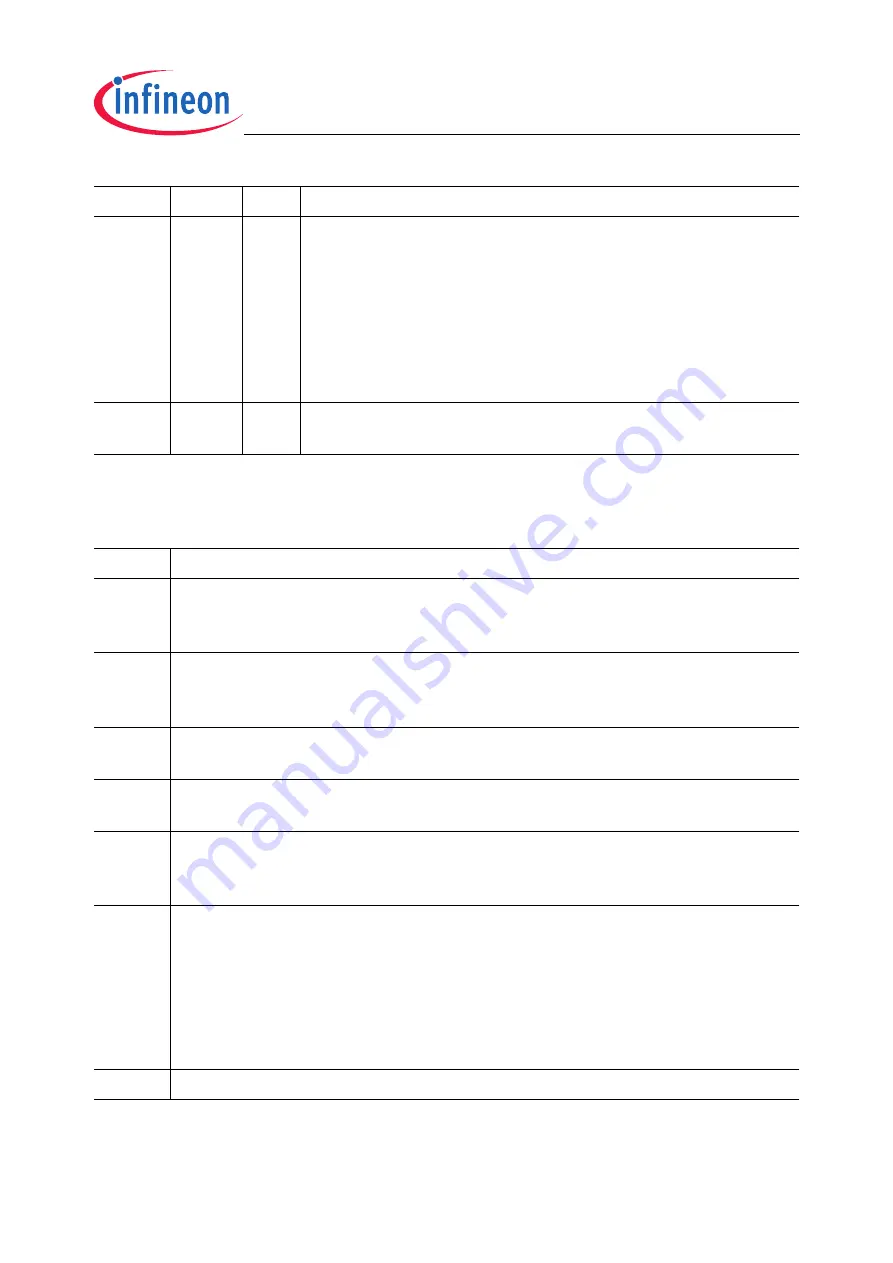

Bit Timing Analysis Modes

CFCOV

23

rwh

CAN Frame Counter Overflow Flag

Flag CFCOV is set upon a frame counter overflow (transition

from FFFF

H

to 0000

H

). In bit timing analysis mode, CFCOV

is set upon an update of CFC. An interrupt request is

generated if CFCIE = 1.

0

No overflow has occurred since last flag reset.

1

An overflow has occurred since last flag reset.

CFCOV must be reset by software.

0

21,

[31:24]

r

Reserved

Read as 0; should be written with 0.

Table 15-9

Bit Timing Analysis Modes (CFMOD = 10)

CFSEL

Measurement

000

B

Whenever a dominant edge (transition from 1 to 0) is monitored on the

receive input, the time (measured in clock cycles) between this edge and the

most recent dominant edge is stored in CFC.

001

B

Whenever a recessive edge (transition from 0 to 1) is monitored on the

receive input, the time (measured in clock cycles) between this edge and the

most recent dominant edge is stored in CFC.

010

B

Whenever a dominant edge is received as a result of a transmitted dominant

edge, the time (clock cycles) between both edges is stored in CFC.

011

B

Whenever a recessive edge is received as a result of a transmitted recessive

edge, the time (clock cycles) between both edges is stored in CFC.

100

B

Whenever a dominant edge that qualifies for synchronization is monitored on

the receive input, the time (measured in clock cycles) between this edge and

the most recent sample point is stored in CFC.

101

B

With each sample point, the time (measured in clock cycles) between the

start of the new bit time and the start of the previous bit time is stored in

CFC[11:0].

Additional information is written to CFC[15:12] at each sample point:

CFC[15]: Transmit value of actual bit time

CFC[14]: Receive sample value of actual bit time

CFC[13:12]: CAN bus information (see

111

B

Reserved, do not use this combination.

Field

Bits

Type Description

*