78

78

78

78

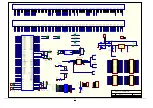

(7) Hardware Breakpoint Control Register

7

6

5

4

3

2

1

0

Address:C4

H

---

---

---

---

---

HBI

BONWR BONRD

Read/Write

(---)

(---)

(---)

(---)

(---)

(R/W)

(R/W)

(R/W)

Initial Value

(---)

(---)

(---)

(---)

(---)

(X)

(0)

(0)

Interrupt

INT0

can be generated when external bus address matches value in

Hardware Breakpoint Address Registers and when minimum one of

BONWR

(Break on Write) or

BONRD

(Break on Read) are ”1”. Interrupt is generated as

positive impulse (”0”->”1”->”0”).

When the BONWR='0' and BONRD='0' and UKIE='0', the INT0 pin will stay in

high impedance state with only 47k pullup connected to it.

[Bit 2]

HBI

– this bit can be used to distinguish if the INT0 interrupt was caused

by the Hardware breakpoint or the User Key. If HBI=1, the interrupt was caused

by the Hardware breakpoint. If HBI=0, the interrupt was caused by the User

Key. If both HBI and UKI (see the Hardware Status register) are log. ‘1’, the

interrupt was caused by both pressing the User Key and the Hardware

breakpoint.

Note: only addresses A0-15 are compared when small model is selected

(System Configuration Register).

(8) Hardware Breakpoint Address Registers

7

6

5

4

3

2

1

0

Address: C5

H

A7

A6

A5

A4

A3

A2

A1

A0

Read/Write

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

Initial Value

(?)

(?)

(?)

(?)

(?)

(?)

(?)

(?)

7

6

5

4

3

2

1

0

Address:C6

H

A15

A14

A13

A12

A11

A10

A9

A8

Read/Write

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

Initial Value

(?)

(?)

(?)

(?)

(?)

(?)

(?)

(?)

7

6

5

4

3

2

1

0

Address:C7

H

A23

A22

A21

A20

A19

A18

A17

A16

Read/Write

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

(R/W)

Initial Value

(?)

(?)

(?)

(?)

(?)

(?)

(?)

(?)

(9) Hardware Status Register

7

6

5

4

3

2

1

0

Address:C8

H

---

---

---

---

UKEY

UKI

UKIE

MSEL

Read/Write

---

---

---

---

---

R

(R/W)

(R)

Initial Value

(---)

(---)

(---)

(---)

(---)

(0)

(0)

(X)

[Bit 0]

MSEL

– this bit holds the value of the MSEL jumper J10. When the

jumper is short, this bit is ‘0’, otherwise it is ‘1’. When both the PE kernel

and Fujitsu Softune monitor are present in the external FLASH memory,