among them:

NO=2 PLLDO

1M<XTAL/ PLLN<25MHz;

200MHz<CLK×NO<1000MHz;

PLLM>1;PLLN>1;

By setting bit 7 of the 0x0C register to 1, the PLL can be bypassed. At this time, the PLL output is

CLK=XTALI;

Configure bit 0 of 0x0C to 1 or the PWD pin of the chip is pulled high to put the PLL into sleep

state. At this time, the PLL has no clock output.

Configure bit 7 (Clk_in_sel) of Register 0x0A as 1, and CLK does not select the output clock of the

PLL. Instead, choose XTALI directly, which is CLK=XTALI.

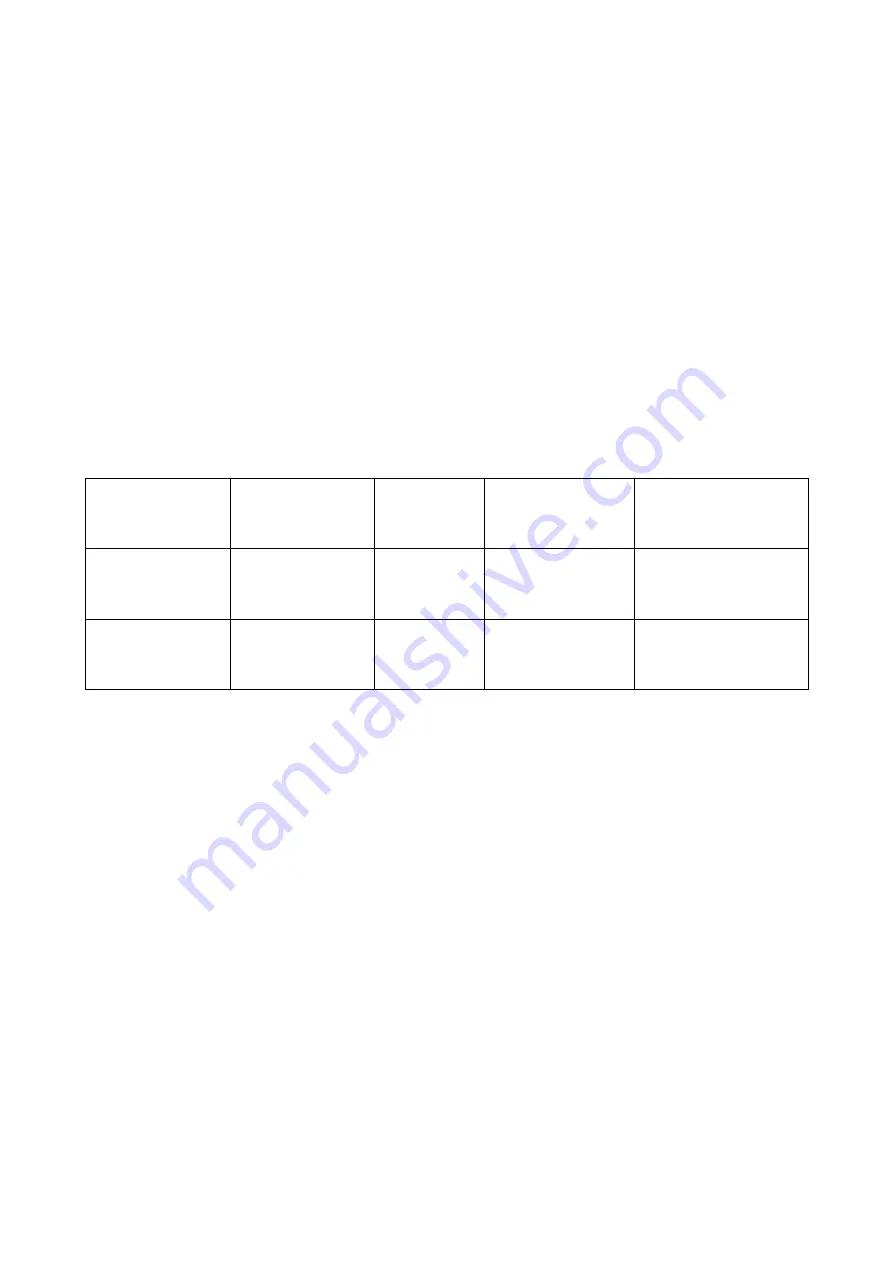

Table 4.1 recommends two typical PLL output clock configuration parameters

XTALI

PLL configuration

parameters

PLL output

clock

System clock

configuration

parameter

System output clock

12.288M

Reg0x0B = 0x40

Reg0x0C = 0x32

49.152M

Reg0xB9 = 0x05

Reg0xBA = 0x04

Reg0xBB = 0x02

Sys_clk=9.8304

Clk_codec=12.288M

CLKOUT=24.576M

29.4912M

Reg0x0B = 0x28

Reg0x0C = 0x33

49.152M

Reg0xB9 = 0x05

Reg0xBA = 0x04

Reg0xBB = 0x02

Sys_clk=9.8304

Clk_codec=12.288M

CLKOUT=24.576M

4.4 Chip parameter configuration interface

The MCU uses the U_SPI port to perform parameter configuration, status control information, and

write/receive data to and from the HR_C6000, and performs corresponding interrupt processing

according to the TIME_SLOT_INTER, SYS_INTER, RF_TX_INTER, and RF_RX_INTER

interrupts given by the HR_C6000. The MCU can also control the Sleep state of the chip through

the GPIO pins. Its interface is shown below.