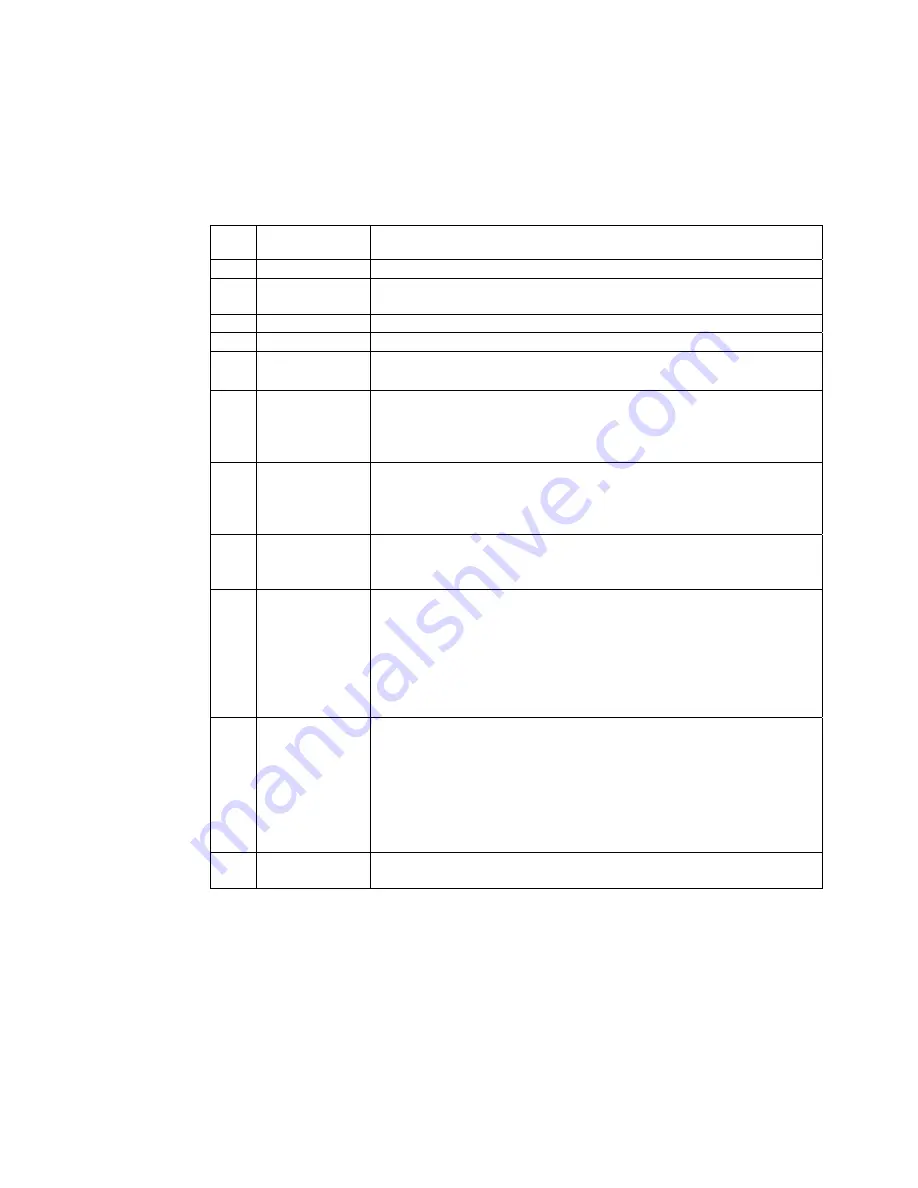

Item Check

When

Completed

Description

14

The Neuron Chip CLK2 pin is not connected.

15

The Neuron Chip and PLT-22 transceiver are placed adjacent

to one another on the same printed circuit board.

16

The length of the ~RESET line is

≤

50mm (2").

17

The length of the CKOUT line is

≤

50mm (2").

18

The ground traces and V

DD5

traces between the transceiver

and the Neuron Chip are low impedance.

19

The correct frequency of the CKOUT pin (Neuron Chip CLK1

input) is selected. If the PLT-22 transceiver is used in its dual

frequency mode, the Neuron Chip clock is set to 2.5MHz or

higher.

20

The CKSEL1 pin is connected via a 4.7k

Ω

resistor to the

appropriate supply rail. Do not tie this pin directly to a supply

rail. The CLKSEL0 pin may be tied directly to the appropriate

supply rail.

21

A Low Voltage Interrupt (LVI) circuit with open collector

output (such as the Motorola MC33064) is used to supply a

reset signal to both the Neuron Chip and the transceiver.

22

Two external 56pF capacitors are used, one tied between

~RESET and V

DD5

, the other between ~RESET and GND, are

used, and placed as close as possible to the Neuron Chip

~RESET pin. Total load capacitance on ~RESET line is within

Neuron Chip specification limits taking into account the two

56pF capacitors on the ~RESET line internal to the

transceiver.

23

The transceiver’s TXLVL pin is grounded for most devices

(TXLVL=7Vp-p).

OR

The transceiver’s TXLVL pin is left open (TXLVL=3.5Vp-p)

only if the transceiver is to be used in a CENELEC 116dBµV-

compliant device or if the V

A

supply will be less than 11.4

Volts and power management is disabled.

24

PLT-22 SIP not touching any electrically conductive adjacent

components or chassis.

L

ON

W

ORKS

PLT-22 Transceiver User’s Guide

B-3

Summary of Contents for LONWORKS PLT-22

Page 6: ...iv Echelon...

Page 14: ...1 8 Introduction...

Page 67: ...LONWORKS PLT 22 Transceiver s User Guide 5 7 Figure 5 3 Capacitor Input Power Supply Schematic...

Page 92: ...6 10 Design and Test for Electromagnetic Compatibility...

Page 110: ...7 18 Communication Performance Verification...

Page 114: ...8 4 References...

Page 118: ...A 4 Appendix A...