17

Avago Technologies Confidential

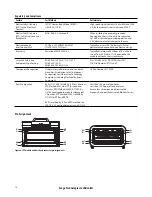

CXP Two-Wire Serial Interface Timing Specifications

Parameter

Symbol

Min

Max

Unit

Condition

Clock Frequency

f

SCL

0

400

kHz

Clock Pulse Width Low

t

LOW

1.3

m

s

Clock Pulse Width High

t

HIGH

0.6

m

s

Time bus free before new transmission can start

t

BUF

20

m

s

Note 1

START Set-up Time

t

SU,STA

0.6

m

s

START Hold Time

t

HD,STA

0.6

m

s

Data Set-up Time

t

SU,DAT

0.1

m

s

Note 2

Data Hold Time

t

HD,DAT

0

m

s

Note 3

SDA and SCL rise time

t

R,400

0.3

m

s

Note 4

SDA and SCL fall time

t

F,400

0.3

m

s

Note 5

STOP Set-up Time

t

SU,STO

0.6

m

s

Notes:

1. Between STOP & START and between ACK & ReSTART.

2. Data In Set Up Time is measured from Vil(max)SDA or Vih(min)SDA to Vil(max)SCL.

3. Data In Hold Time is measured from Vil(max)SCL to Vil(max)SDA or Vih(min)SDA.

4. Rise Time is measured from Vol(max)SDA to Voh(min)SDA.

5. Fall Time is measured from Voh(min)SDA to Vol(max)SDA.

Memory Specifications

Memory may be accessed in single-byte or multi-byte (up to 4 bytes) memory blocks. The largest multiple-byte contigu-

ous write operation that a module shall handle is 4 bytes. The minimum size write block is 1 byte.

Memory Transaction Timing Specification

Parameter

Symbol

Min

Max

Unit

Condition

Serial Interface Clock Holdoff - “Clock Stretching”

T_clock_hold

500

m

s

Note 1

Complete Single or Sequential Write

t

WR

40

ms

Note 2

Endurance (Write cycles)

50,000

75,000

cycles

Note 3

Notes:

1. Maximum time the CXP module may hold the SCL line low before continuing with a read or write operation.

2. Complete up to 4 Byte write. Timing should start from Stop bit at the end of the sequential write operation and continue until the module responds

to another operation.

3. 50 K write cycles at 70°C.