13

Avago Technologies Confidential

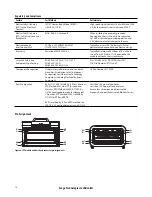

Pin

Signal Name

Signal Description

Logic

Notes

C1

GND

Ground

C2

RX1p

Receiver Non-Inverted Data Output

CML-O

C3

RX1n

Receiver Inverted Data Output

CML-O

C4

GND

Ground

C5

RX3p

Receiver Non-Inverted Data Output

CML-O

C6

RX3n

Receiver Inverted Data Output

CML-O

C7

GND

Ground

C8

RX5p

Receiver Non-Inverted Data Output

CML-O

C9

RX5n

Receiver Inverted Data Output

CML-O

C10

GND

Ground

C11

RX7p

Receiver Non-Inverted Data Output

CML-O

C12

RX7n

Receiver Inverted Data Output

CML-O

C13

GND

Ground

C14

RX9p

Receiver Non-Inverted Data Output

CML-O

C15

RX9n

Receiver Inverted Data Output

CML-O

C16

GND

Ground

C17

RX11p

Receiver Non-Inverted Data Output

CML-O

C18

RX11n

Receiver Inverted Data Output

CML-O

C19

GND

Ground

C20

PRSNT_L

Module Present

O

1

C21

Int_L/Reset_L

Interrupt / Reset

I/O

2

D1

GND

Ground

D2

RX0p

Receiver Non-Inverted Data Output

CML-O

D3

RX0n

Receiver Inverted Data Output

CML-O

D4

GND

Ground

D5

RX2p

Receiver Non-Inverted Data Output

CML-O

D6

RX2n

Receiver Inverted Data Output

CML-O

D7

GND

Ground

D8

RX4p

Receiver Non-Inverted Data Output

CML-O

D9

RX4n

Receiver Inverted Data Output

CML-O

D10

GND

Ground

D11

RX6p

Receiver Non-Inverted Data Output

CML-O

D12

RX6n

Receiver Inverted Data Output

CML-O

D13

GND

Ground

D14

RX8p

Receiver Non-Inverted Data Output

CML-O

D15

RX8n

Receiver Inverted Data Output

CML-O

D16

GND

Ground

D17

RX10p

Receiver Non-Inverted Data Output

CML-O

D18

RX10n

Receiver Inverted Data Output

CML-O

D19

GND

Ground

D20

VCC3.3-RX

+3.3 V Power supply receiver

D21

Not used

Not used , 3.3 V only

Notes:

1. Shorted directly to GND inside the module.

2. Int_L/Reset_L is a bidirectional contact. When driven from the host, it operates logically as a Reset signal (input). When driven from the module, it

operates logically as an Interrupt signal (output). Signal levels are per specified in Low Speed Logic section. Host shall use a pull up of 1.5 kohm – 10

kohm to Vcc3.3 for this pin.