14

Avago Technologies Confidential

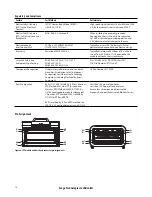

Control Interface

The control interface includes a bi-directional Int_L/

Reset_L interrupt/reset signal and two-wire serial – SCL

(clock) and SDA (data) signals to provide users rich func-

tionality over an efficient and easily used interface. The

TWS interface is implemented as a slave device and com-

patible with industry standard two-wire serial protocol.

Signal and timing characteristics are further defined in

this section. In general, TWS bus timing and protocols

follow the implementation popularized in Atmel Two-wire

Serial EEPROMs.

Low-Speed Electrical Contact Definitions

SDA, SCL

SCL is the clock of the two-wire serial interface, and SDA is

the data for the two-wire interface. SCL and SDA must be

pulled up in the host through a pull-up resistor of value

appropriate to the overall bus capacitance and the rise

and fall time requirements as per “CXP two-wire Serial

Interface Timing Specifications” table.

The host supplied SCL input to the CXP transceiver is used

to positive-edge clock data into each CXP device and neg-

ative-edge clock data out of each device. CXP transceivers

operate only as slave devices. The host must provide a bus

master for SCL and initiate all read/write communication.

Since all CXP transceivers use the same two base

addresses, each CXP port requires its own SCL/SDA bus.

Support of multiple ports in a host requires multiple SCL/

SDA buses, or multiplexing circuitry such as a multiplexer

chip or a switch chip.

INT_L/RESET_L

Int_L/Reset_L is a bidirectional contact. When driven

from the host, it op erates logically as a Reset signal.

When driven from the module, it oper ates logically as an

Interrupt signal. In both cases, the signal is asserted low,

as indicated by the ’_L’ suffix. The Int_L/Reset_L signal

requires open collector outputs in both the host and

the module, and must be pulled up on the host board

with 1.5 kohm – 10 kohm resistor. The two uses are

distinguished by timing – a shorter assertion, driven by

the module indicates an interrupt and a longer assertion

of the signal driven by the host indicates a reset as per “I/O

Timing for Control and Status Functions” Table below.

Int_L operation:

When Int_L/Reset_L is pulled “Low” by the module for

longer than the minimum pulse width (t

Int_L, PW-min

) and

shorter than the maximum pulse width (t

Int_L, PW-max

) the

signal signifies an interrupt. When asserted “Low”, Int_L

indicates a possible module operational fault or a status

critical to the host system. The host identifies the cause

of the interrupt using the two-wire serial interface. Int_L

must operate in Pulse mode (as opposed to Static mode),

in order to distinguish a short Int_L signal from a longer

Reset_L signal, so the module must de-assert Int_L/

Reset_L after the interrupt has been signaled.

Reset_L operation:

When the Int_L/Reset_L signal is pulled “Low” by the

host for longer than the minimum reset pulse length

(

t

Reset_L,PW-min

), it ini tiates a complete module reset,

returning all user module settings to their default state.

There is no maximum reset pulse length. Module Reset

Assert Time (t_init) starts on the rising edge after the

low level on the Reset_L signal is released. During the

execution of a reset (t_init) the host shall disregard all

status bits until the module indicates a completion of the

reset interrupt. The module indicates this by posting an

Int_L signal with the Data_Not_Ready bit (Memory Map,

Byte 2, bit 0) negated. Note that on power up (including

hot insertion) the module will post this completion of

reset interrupt without requiring a reset from the host.

PRSNT_L

PRSNT_L is used to indicate when the module it plugged

into the host re ceptacle. PRSNT_L is pulled up to Vcc3.3

on the host board through > 50 k

W

and pulled down

directly to signal common (no re sistor) in the module. The

PRSNT_L is asserted “Low” when inserted and deas serted

“High” when the module is physically absent from the host

con nector.