Unified Fieldbus Controller UFC100-L2 – Basic mode operation

Page 30

Rev. 1.0

Proprietary and confidential information of Aniotek Inc.

21 May 2018

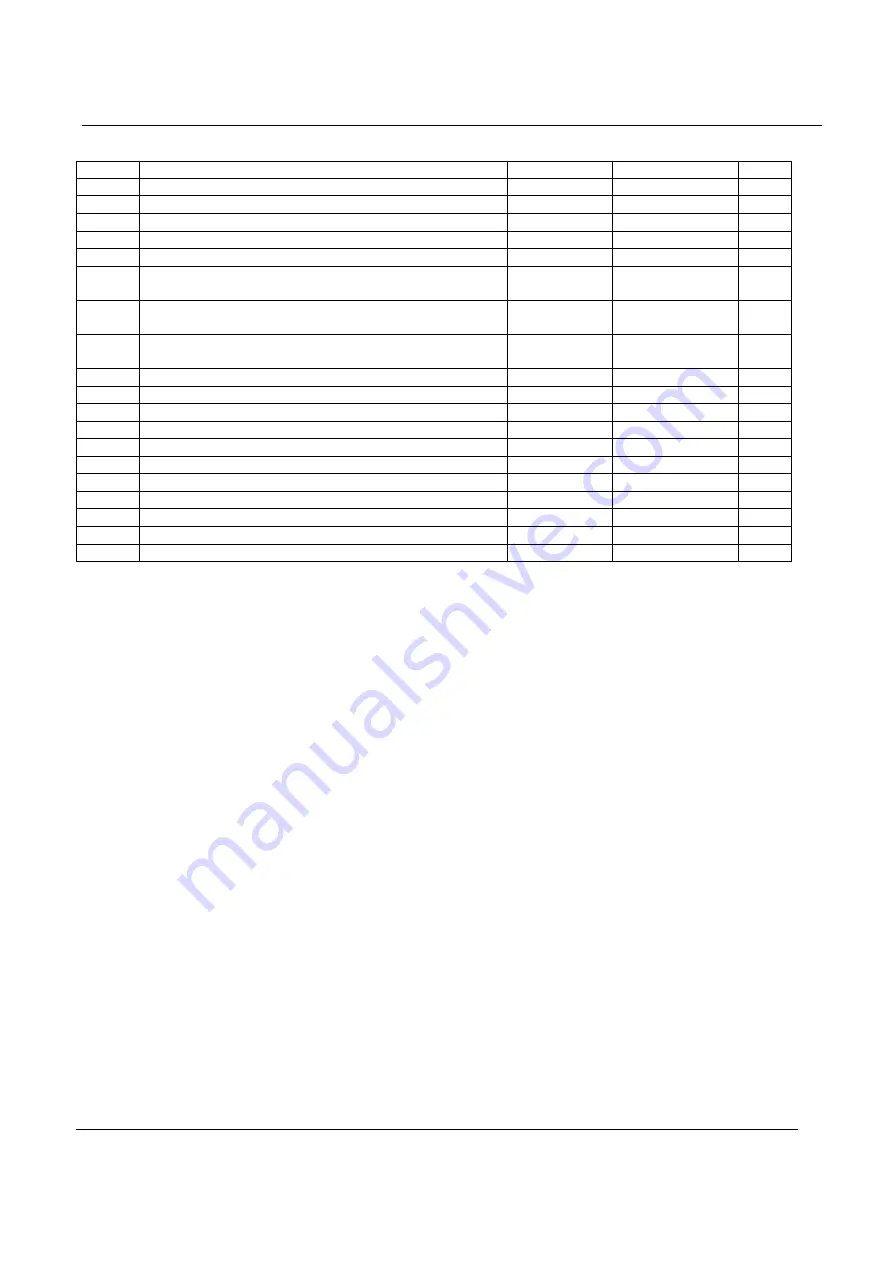

Table 22: Bus Timings for Intel type CPU

Num

Description

Min

Max

Notes

t1

Valid Address to RDn, WRn assertion (setup time)

10

t2

RDn, WRn assertion to invalid Address (hold time)

10

t3

CSn assertion to RDn, WRn assertion setup time

0

t4

RDn, WRn negation to CSn negation (hold time)

0

t5a

RDn, WRn assertion to RDY negation delay

20

3

t5b

RDY negation duration

0

4*TCLK

3*TCLK

1

2

t5c

RDn, WRn assertion to DACKn assertion delay

5

4*TCLK

3*TCLK

1

2

t5d

End of previous cycle to DACKn (RDY) assertion delay

4*TCLK + 30

3*TCLK + 30

3

2

t6

RDn assertion to active Data output delay

20

t7

Valid address to valid data output access delay

30

t8a

RDY (DACKn) to valid Data delay

20

3

t8b

Positive edge of CLKIN to valid Data delay

30

3

t9

RDn negation to tristate Data, invalid Data delay

3

15

t10

RDn, WRn negation to DACKn negation delay

0

15

t11

RDn, WRn assertion duration

10

t12

RDn, WRn inactive time

10

t13

CSn inactive time

10

t14

Valid Data to WRn negation (setup time)

5

t15

WRn negation to invalid Data (hold time)

5

Notes:

1.

This delay depends upon the immediately prior cycle. If there is sufficient gap between the two successive cycles, then

RDY is not negated; DACKn assertion delay is 20 ns. The Write cycles and some of the Read cycles require that the end

of the following cycle be spaced by 4*TCLK.

2.

DACKn (RDY) can be asserted one clock earlier, if configured to do so by software. It requires that the delay from

DACKn (RDY) assertion to RDn, WRn negation be at least one clock.

3.

These delays apply only if RDY is negated. Otherwise, t7 applies. Use t8a only if the CPU cannot use CLKIN to

synchronize the Read data input.