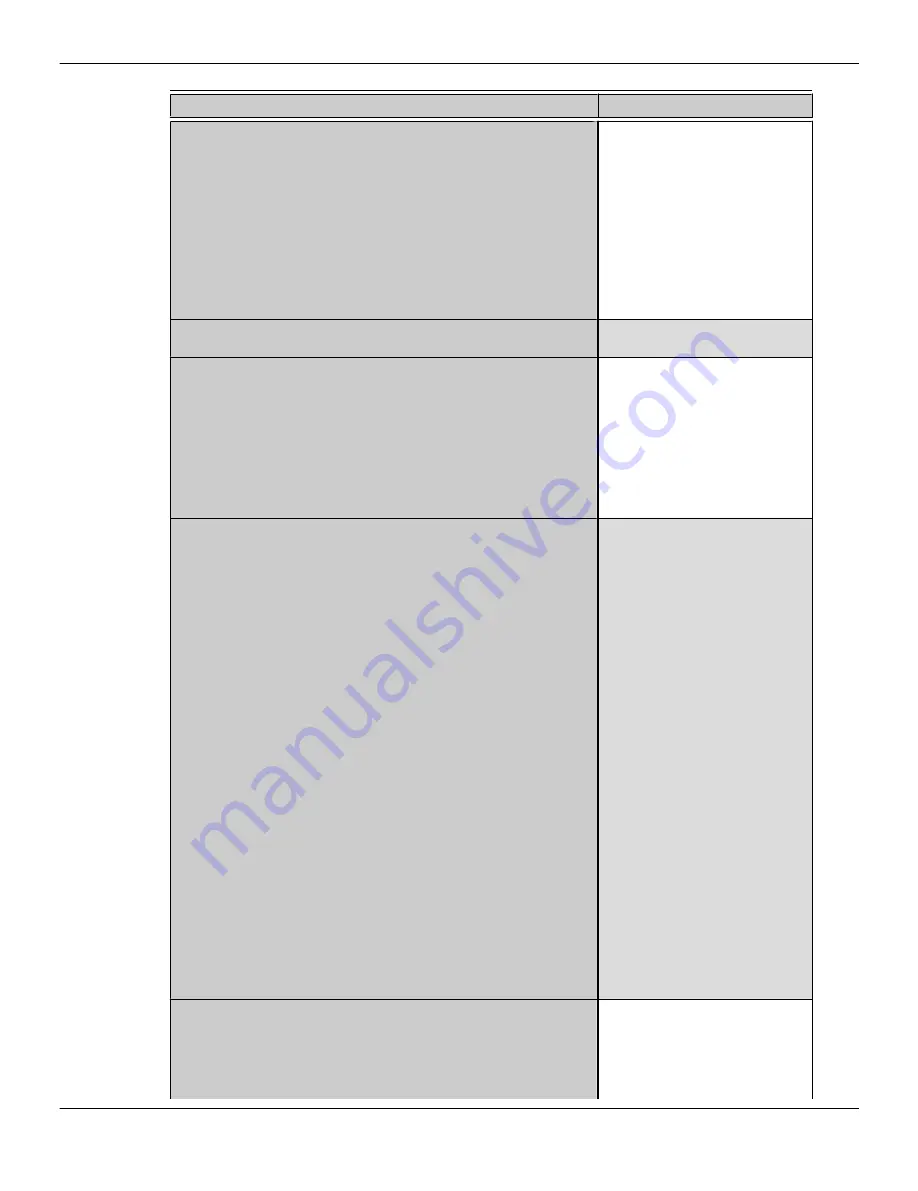

Table 4–4 Registers for Setting Backlight PWM Parameters

Register Field

Description

DISPOUT.LVTMA_PWRSEQ_REF_DIV.BL_PWM_REF_DIV

PWM frequency coarse control.

This 16-bit value specifies the

input reference clock divider. The

frequency of the input reference

clock (REF) is divided down by

this amount specified.

This value represents a divider of

1 to 65536. “0” is a special value

that represents a divider of

65536. Other values (1 to 65535)

map directly to the same divider

value.

DISPOUT.BL_PWM_CNTL.BL_PWM_EN

Set to 1 to enable the PWM signal

generator.

DISPOUT.BL_PWM_CNTL.BL_PWM_FRACTIONAL_EN

Set to 1 to enable fractional active

duty-cycle mode.

When enabled, the active duty

cycle of each backlight period can

vary over time to achieve the

requested active duty cycle (both

integer and fractional

components) specified by the

BL_ACTIVE_INT_FRAC_CNT

value.

DISPOUT.BL_PWM_PERIOD_CNTL.BL_PWM_PERIOD_BITCNT

This 4-bit value has a dual

purpose. First, it specifies the

number of LSBs of the

BL_PWM_PERIOD register used

to represent the backlight period.

The second purpose of this

register is to specify how many

MSBs of the

BL_ACTIVE_INT_FRAC_CNT

register field represent the

integer component of the active

duty cycle. The remaining LSBs of

this register field represent the

fractional component of the active

duty cycle.

For this register field, “0” is a

special value that implies 16 bits

are to be used for the period (and

integer active duty cycle). Other

values of 1 to 15 for this field

directly map to the same number

of bits to be used for the period

(and MSBs of the active duty cycle

as the integer component of the

active duty-cycle value).

When fractional active duty-cycle

mode is enabled, this value should

be programmed to the value that

represents the smallest number

of bits possible to represent the

required backlight period.

DISPOUT.BL_PWM_PERIOD_CNTL.BL_PWM_PERIOD

PWM frequency fine control.

Specifies the period of the

backlight PWM signal. This 16-bit

value represents the number of

divided down input reference

clock ( REF /

Timing Specifications

53

©

2017

Advanced Micro Devices, Inc.

AMD Confidential - Do not duplicate.

"Vega 10" Databook

56006_1.00