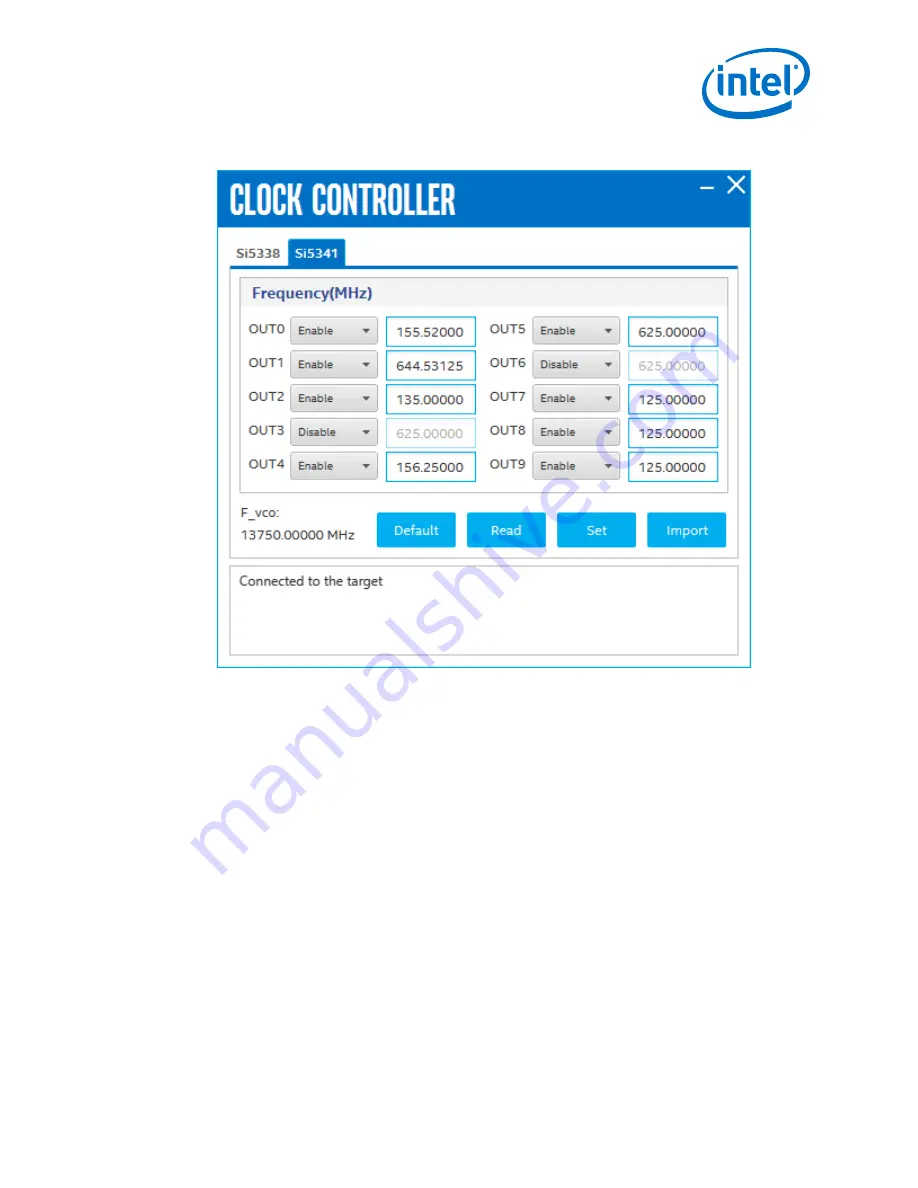

Figure 32.

Clock Controller - Si5341

Si5338 tab and Si5341 tab display the same GUI controls for each clock generators.

Each tab allows for separate control. The Si5338 is capable of synthesizing four

independent user-programmable clock frequencies up to 710 MHz.

The controls of the clock controller are described below:

F_vco

Displays the generating signal value of the voltage-controlled oscillator.

Registers

Display the current frequencies for each oscillator.

Frequency

Allows you to specify the frequency of the clock MHz.

SSC

Set enable or disable Spread Spectrum Clocking.

6. Board Test System

UG-20046 | 2018.07.20

Intel

®

Stratix

®

10 GX FPGA Development Kit User Guide

89