5

5

If you have not already created a Compare file for the previous test (single-clock,

single-edge state acquisition, page 3-31), use the following steps to create one. For

subsequent passes through this test, skip this step and go to step 6.

a

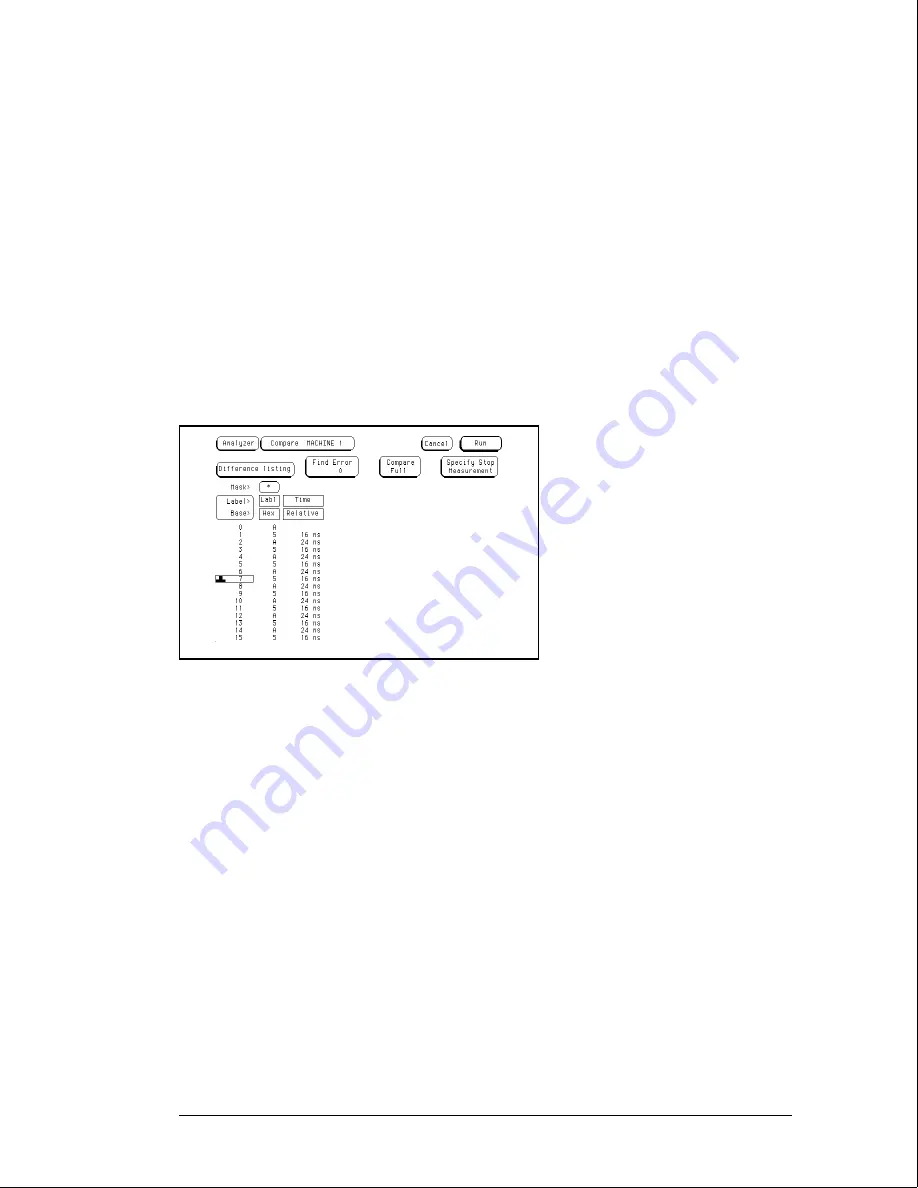

Press Run. The display should show a checkerboard pattern of alternating As and 5s.

Verify the pattern by scrolling through the display.

b

Press the List key. In the pop up menu, use the RPG knob to move the cursor to

Compare. Press Select.

c

In the Compare menu, move the cursor to Copy Listing to Reference, then select

Execute from the pop-up menu and press the Select key.

d

Move the cursor to Specify Stop Measurement and press the Select key. Press Select

again to turn on Compare. At the pop up menu, select Compare. Move the cursor to

the Equal field and press the Select key. At the pop up menu, select Not Equal. Press

Done.

e

Move the cursor to the Reference Listing field and select. The field should toggle to

Difference Listing.

6

Press the blue shift key, then press the Run key. If 2 - 4 acquisitions are obtained

without the "Stop Condition Satisfied" message appearing, then the test passes.

Press Stop to halt the acquisition. Record the Pass or Fail results in the

performance test record.

7

Enable the pulse generator channel 2 COMP (with the LED on).

8

Check the clock pulse width.

a

Enable the pulse generator channel 1 and channel 2 outputs (with the LED off).

b

b

In the oscilloscope Timebase menu, select Delay. Using the oscilloscope knob,

position the clock waveform so that the waveform is centered on the screen.

c

In the oscilloscope Delta V menu, set the Marker 1 Position to Chan 2, then set

Marker 1 at

−

1.3000 V. Set the Marker 2 Position to Chan 2, then set Marker 2 at

−

1.3000 V.

d

In the oscilloscope Delta T menu, select Start On Neg Edge 1. Select Stop On Pos

Edge 1.

e

If the pulse width is outside of the limits, adjust the pulse generator channel 2 width

and select the oscilloscope Precision Edge Find until the pulse width is within limits.

Testing Performance

To test the multiple-clock, multiple-edge, state acquisition

3–42

Summary of Contents for 1664A

Page 3: ...The Agilent Technologies 1664A Logic Analyzer iii...

Page 8: ...Contents viii...

Page 22: ...2 6...

Page 91: ...Troubleshooting Flowchart 1 Troubleshooting To use the flowcharts 5 3...

Page 92: ...Troubleshooting Flowchart 2 Troubleshooting To use the flowcharts 5 4...

Page 93: ...Troubleshooting Flowchart 3 Troubleshooting To use the flowcharts 5 5...

Page 94: ...Troubleshooting Flowchart 4 Troubleshooting To use the flowcharts 5 6...

Page 95: ...Troubleshooting Flowchart 5 Troubleshooting To use the flowcharts 5 7...

Page 96: ...Troubleshooting Flowchart 6 Troubleshooting To use the flowcharts 5 8...

Page 97: ...Troubleshooting Flowchart 7 Troubleshooting To use the flowcharts 5 9...

Page 98: ...Troubleshooting Flowchart 8 Troubleshooting To use the flowcharts 5 10...

Page 99: ...Troubleshooting Flowchart 9 Troubleshooting To use the flowcharts 5 11...

Page 100: ...Troubleshooting Flowchart 10 Troubleshooting To use the flowcharts 5 12...

Page 101: ...Troubleshooting Flowchart 11 Troubleshooting To use the flowcharts 5 13...

Page 102: ...Troubleshooting Flowchart 12 Troubleshooting To use the flowcharts 5 14...

Page 124: ...Exploded View of the 1664A Replacing Assemblies 6 4...

Page 137: ...Exploded View Exploded view of the 1664A logic analyzer Replaceable Parts Exploded View 7 3...

Page 160: ...8 18...

Page 162: ......