60

VC707 Evaluation Board

UG885 (v1.2) February 1, 2013

Chapter 1:

VC707 Evaluation Board Features

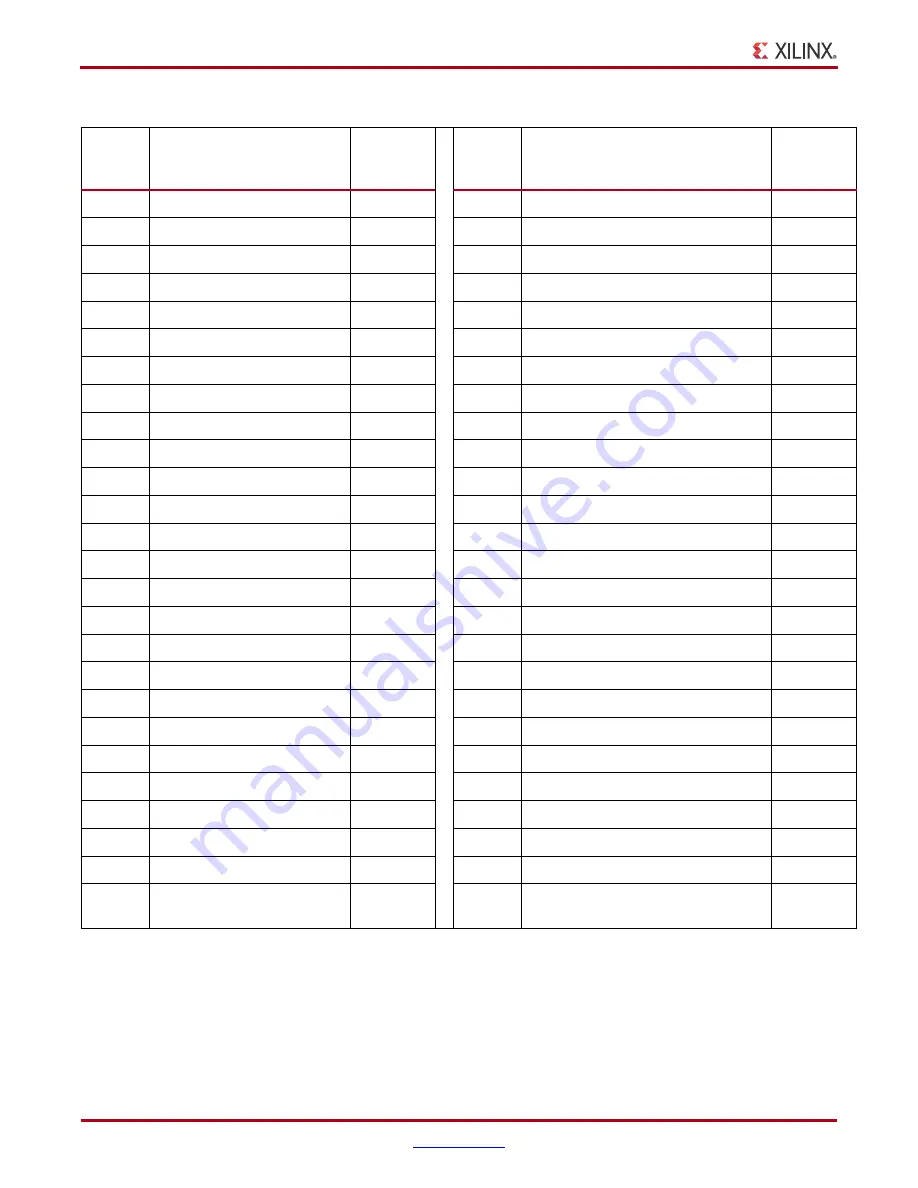

lists the connections between the FMC2 HPC J37 connector and the FPGA U1.

Note:

The FMC2 HPC HB00-HB21 pair connections are not available with the

XC7VX485T-2FFG1761C FPGA installed on the VC707. Refer to the Virtex-7 FPGA VC707

Evaluation Kit Master Answer Record in

for more information.

J2

NC

K1

NC

J3

NC

K4

NC

J6

FMC1_HPC_HA03_P

H33

K5

NC

J7

FMC1_HPC_HA03_N

G33

K7

FMC1_HPC_HA02_P

E33

J9

FMC1_HPC_HA07_P

C38

K8

FMC1_HPC_HA02_N

D33

J10

FMC1_HPC_HA07_N

C39

K10

FMC1_HPC_HA06_P

G36

J12

FMC1_HPC_HA11_P

J37

K11

FMC1_HPC_HA06_N

G37

J13

FMC1_HPC_HA11_N

J38

K13

FMC1_HPC_HA10_P

H38

J15

FMC1_HPC_HA14_P

E37

K14

FMC1_HPC_HA10_N

G38

J16

FMC1_HPC_HA14_N

E38

K16

FMC1_HPC_HA17_CC_P

C35

J18

FMC1_HPC_HA18_P

F39

K17

FMC1_HPC_HA17_CC_N

C36

J19

FMC1_HPC_HA18_N

E39

K19

FMC1_HPC_HA21_P

D37

J21

FMC1_HPC_HA22_P

F36

K20

FMC1_HPC_HA21_N

D38

J22

FMC1_HPC_HA22_N

F37

K22

FMC1_HPC_HA23_P

B36

J24

FMC1_HPC_HB01_P

H28

K23

FMC1_HPC_HA23_N

B37

J25

FMC1_HPC_HB01_N

H29

K25

FMC1_HPC_HB00_CC_P

J25

J27

FMC1_HPC_HB07_P

G26

K26

FMC1_HPC_HB00_CC_N

J26

J28

FMC1_HPC_HB07_N

G27

K28

FMC1_HPC_HB06_CC_P

K23

J30

FMC1_HPC_HB11_P

K22

K29

FMC1_HPC_HB06_CC_N

J23

J31

FMC1_HPC_HB11_N

J22

K31

FMC1_HPC_HB10_P

M22

J33

FMC1_HPC_HB15_P

M21

K32

FMC1_HPC_HB10_N

L22

J34

FMC1_HPC_HB15_N

L21

K34

FMC1_HPC_HB14_P

J21

J36

FMC1_HPC_HB18_P

G21

K35

FMC1_HPC_HB14_N

H21

J37

FMC1_HPC_HB18_N

G22

K37

FMC1_HPC_HB17_CC_P

M24

K38

FMC1_HPC_HB17_CC_N

L24

J39

FMC1_VIO_B_M2C

BANK 36

VCCO

K40

FMC1_VIO_B_M2C

BANK 36

VCCO

Table 1-27:

J35 VITA 57.1 FMC 1 HPC Connections

(Cont’d)

J35

FMC 1

HPC Pin

Schematic Net Name

U1 FPGA

Pin

J35

FMC 1

HPC Pin

Schematic Net Name

U1 FPGA

Pin

Содержание VC707

Страница 1: ...VC707 Evaluation Board for the Virtex 7 FPGA User Guide UG885 v1 2 February 1 2013...

Страница 74: ...74 www xilinx com VC707 Evaluation Board UG885 v1 2 February 1 2013 Chapter 1 VC707 Evaluation Board Features...

Страница 94: ...94 www xilinx com VC707 Evaluation Board UG885 v1 2 February 1 2013 Appendix D Board Setup...

Страница 96: ...96 www xilinx com VC707 Evaluation Board UG885 v1 2 February 1 2013 Appendix E Board Specifications...