VXI Technology, Inc.

44

SMP7500 Programming

E

XAMPLE OF A

P

ORT

S

ET AS AN

O

UTPUT

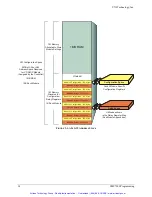

In this example the SMP7500 will be set up to run in double buffered mode. Data will be loaded

into the unit, and output when it receives the UUT generated F/P CLK edge. The SMP7500 will

output one 8-bit byte to the UUT from a port.

USER CONNECTOR

DATA

GND_CLK

GLOBAL

CLK

Off To All Other Ports

47K

User Selectable

HW Jumpers

120

100pf

2

2

Output

Drivers

Over

Current

Sense /

Control

Over Current Sense

Shut Down

ISENSE

Double

Buffered

Latched

Output

Data

Buffer

R/B

Control

Writes to

Specific Port

Addresses

Control

Control

Relay Req. 000Ch Write Event

WR EVENT

R/B

I/O Data

Buffer

Data

Control

SMIP INTERFACE

MODULE

DATA

ADDRESS

CONTROL

BUSYN

TTL

TRIGGER

BUS

0-7

DATA

ADDRESS

CONTROL

V

X

I

BAC

KPL

AN

E

SMP7500 MODULE

Over Current

Reset

Control

Trace

Memory

Backplane Load

F

IGURE

3-2:

O

UTPUT

B

LOCK

D

IAGRAM

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com