VXI Technology, Inc.

14

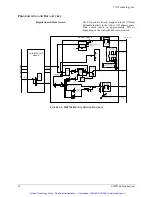

SMP7500 Introduction

P

ROGRAMMING AND

D

ATA

A

CCESS

Register-based Data Access:

The I/O ports are directly mapped into the VXI user

definable registers in the A24 or A32 address space.

Data access occurs in approximately 500 ns,

depending on the controller and software used.

USER CONNECTOR

GND_I/O

CLAMP

DATA

GND_CLK

GLOBAL

CLK

47k

User Selectable

HW Jumpers

22

User Configurable 100K

Pull-Up Resistor Network (SIP)

+5V +12V +24V

User Selectable

HW Jumpers

Fly

B

ack

P

rotec

tion

D

io

de

Off To All Other Ports

47K

User Selectable

HW Jumpers

120

100pf

2

2

Polarity Enable

200K

33K

Output

Drivers

Over

Current

Sense /

Control

Over Current Sense

Shut Down

ISENSE

Immediate

Double

Buffered

Latched

Output

Data

Buffer

Polarity

R/B

Control

Writes to

Specific Port

Addresses

Control

Control

Relay Req. 000Ch Write Event

WR EVENT

R/B

I/O Data

Buffer

Data

Backplane Load

Transparent

Polarity

Control

Control

All Other

Available F/P

CLK Lines

Control

WR Event

Relay Req. 000Ch Write Event

Control

Polarity

SMIP INTERFACE

MODULE

DATA

ADDRESS

CONTROL

BUSYN

TTL

TRIGGER

BUS

0-7

DATA

ADDRESS

CONTROL

VXI

BA

CKP

L

ANE

SMP7500 MODULE

Over Current

Reset

Control

Trace

Memory

F

IGURE

1-3:

SMP7500

M

ODULE

B

LOCK

D

IAGRAM

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com