TOSHIBA

TMPR3904F Rev. 2.0

165

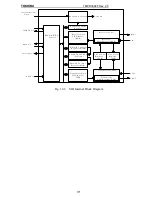

11.3.2

Interrupt detection

The active status of an interrupt by the INT[7:0] can be set up in the EIM field of the CConR.

There are the high level, low level, rising edge, and falling edge in the active status. The

TX3904 interrupt detection circuit notifies of an interrupt request to the TX39 Processor Core or

the IRC when it has acknowledged the set up status.

Negating of an interrupt signal should be done in the interrupt handler after confirming the

interrupt source. When the active status is set up at the high level or the low level, operate for

the external circuit that is asserting the INTn signal to deassert it. When the active status is set

up at the rising edge or the falling edge, negate the interrupt by writing in the value that supports

the ElClr of the CConR.

11.3.3 Interrupt priority arbitration process

This section describes the Numbers 0-15 interrupts that are arbitrated by the IRC.

16 interrupt sources

Arbitrates interrupt requests of the nine internal sources and seven external sources.

Seven interrupt levels

Has seven levels of priority and can set up the priority for each interrupt source.

The interrupt level is set up in the interrupt level register. There is a 3-bit level set-up field for

each interrupt source. The greater the value (the interrupt level) in this field is, the higher the

priority is. When the value is 000 (the interrupt level 0), the interrupt by the source does not

occur.

Interrupt mask

Other than setting-up 000 to the interrupt level, masking by the interrupt mask register is also

possible. If the interrupt level is equal to or less than the value that is set up in the interrupt

mask register, the interrupt shall be masked and shall not be informed to the TX39.

Interrupt source notice

When an interrupt occurs, the IRC informs the TX39 Processor Core of the of the interrupt

number. The TX39 Processor Core can know the interrupt source by reading-out the value in

the IP field of the cause register. When an interrupt from among the Numbers 0-15, the IP[4] is

set to 1, and at the same time, the interrupt number is indicated in IP[3:0].

When multiple interrupts (of the same level) are occurring simultaneously, the source with the

greater source number is informed. Interrupt requests by the INT[0] are informed to the TX39

without going through the IRC so that an interrupt by the INT[0] and another interrupt issue

requests simultaneously. In such a case, implement a priority process by the software.

When once the IRC informs the TX39 of the interrupt source, the interrupt number to be

informed does not change until the process for the interrupt completes (until the corresponding

interrupt status bit becomes 1). When the process has completed, the interrupt number with the

highest priority at that point shall be informed.

Содержание TMPR3904F

Страница 1: ...Users Manual 32bit RISC Microprocessor TX39 family TMPR3904F Rev 2 0 Jan 12 1998 ...

Страница 2: ......

Страница 9: ...Users Manual 01 1 INTRODUCTION 1 1 Overview ...

Страница 10: ...Users Manual 02 1 2 Notation used in this manual Mathematical notation Data notation Signal notation ...

Страница 11: ...Users Manual 03 1 3 Kind of accessing by the TX3904 ...

Страница 12: ...Users Manual 04 1 4 Precautions in the TMPR3904F specification Don t set Don t use ...

Страница 13: ...Users Manual 05 Do not use ...

Страница 14: ...Users Manual 06 ...

Страница 15: ...Users Manual 7 2 FEATURES n n n n n n n n n n n n n ...

Страница 16: ...Users Manual 8 ...

Страница 18: ...Users Manual 10 ...

Страница 19: ...Users Manual 11 4 PINS 4 1 Positions of Pins ...

Страница 20: ...Users Manual 12 ...

Страница 21: ...Users Manual 13 4 2 Functions of Pins ...

Страница 22: ...Users Manual 14 ...

Страница 23: ...Users Manual 15 ...

Страница 24: ...Users Manual 16 ...

Страница 26: ...Users Manual 18 5 2 Register Map ...

Страница 27: ...Users Manual 19 ...

Страница 28: ...Users Manual 20 ...

Страница 30: ...Users Manual 22 5 3 2 PIO2 and PIO1 ...

Страница 32: ...Users Manual 24 5 3 4 Connection of external bus master 5 3 5 INT 7 0 active status clear ...

Страница 33: ...Users Manual 25 5 3 6 INT 7 0 active status set up ...

Страница 34: ...Users Manual 26 ...

Страница 123: ...TOSHIBA TMPR3904F Rev 2 0 115 26 ...

Страница 169: ...TOSHIBA TMPR3904F Rev 2 0 161 26 ...

Страница 203: ...TOSHIBA TMPR3904F Rev 2 0 195 ...

Страница 230: ......