7.2.2 Absence register access............................................................................................................. 41

7.2.3 Time-out error........................................................................................................................... 41

7.3

16-bit Bus Mode................................................................................................................................. 43

7.4

Half Speed Bus Mode ........................................................................................................................ 45

7.5

Bus Arbitration................................................................................................................................... 46

7.5.1 Bus ownership granted.............................................................................................................. 46

7.5.2 Release of bus ownership.......................................................................................................... 47

7.5.3 Kinds of bus ownership ............................................................................................................ 48

7.5.4 Snoop function........................................................................................................................... 49

7.6

Interrupts ........................................................................................................................................... 50

7.6.1 INT[7:0].................................................................................................................................... 50

7.6.2 NMI*......................................................................................................................................... 50

7.7

Reset................................................................................................................................................... 50

8

DRAM CONTROLLER (DRAMC) ............................................................................................................. 51

8.1

Features .............................................................................................................................................. 51

8.2

Block Diagrams.................................................................................................................................. 52

8.3

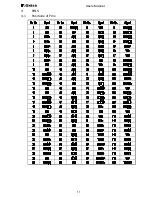

Registers............................................................................................................................................. 53

8.4

Explanations of Registers................................................................................................................... 54

8.4.1 Channel control register 0 (DCCR0) ......................................................................................... 54

8.4.2 Base address mask register 0 (DBMR0).................................................................................... 56

8.4.3 Wait register 0 (DWR0)............................................................................................................. 57

8.4.4 Channel control register 1 (DCCR1) ......................................................................................... 59

8.4.5 Base address mask register 1 (DBMR1).................................................................................... 61

8.4.6 Wait register 1 (DWR1)............................................................................................................. 62

8.4.7 Refresh control register (DREFC) ............................................................................................. 64

8.5

Operations .......................................................................................................................................... 65

8.5.1 Channel select ............................................................................................................................ 65

8.5.2 Address multiplex ...................................................................................................................... 66

8.5.3 Operation modes ........................................................................................................................ 67

8.5.4 32/16-bit static bus sizing .......................................................................................................... 68

8.5.5 Support for external bus master ................................................................................................. 68

8.5.6 Support for half speed bus ......................................................................................................... 68

8.5.7 Page mode support and page hit detection................................................................................ 69

8.5.8 Column address counter............................................................................................................. 69

8.5.9 Timing control .......................................................................................................................... 69

8.5.10 Refresh timing.......................................................................................................................... 69

8.5.11 Arbiter...................................................................................................................................... 70

Содержание TMPR3904F

Страница 1: ...Users Manual 32bit RISC Microprocessor TX39 family TMPR3904F Rev 2 0 Jan 12 1998 ...

Страница 2: ......

Страница 9: ...Users Manual 01 1 INTRODUCTION 1 1 Overview ...

Страница 10: ...Users Manual 02 1 2 Notation used in this manual Mathematical notation Data notation Signal notation ...

Страница 11: ...Users Manual 03 1 3 Kind of accessing by the TX3904 ...

Страница 12: ...Users Manual 04 1 4 Precautions in the TMPR3904F specification Don t set Don t use ...

Страница 13: ...Users Manual 05 Do not use ...

Страница 14: ...Users Manual 06 ...

Страница 15: ...Users Manual 7 2 FEATURES n n n n n n n n n n n n n ...

Страница 16: ...Users Manual 8 ...

Страница 18: ...Users Manual 10 ...

Страница 19: ...Users Manual 11 4 PINS 4 1 Positions of Pins ...

Страница 20: ...Users Manual 12 ...

Страница 21: ...Users Manual 13 4 2 Functions of Pins ...

Страница 22: ...Users Manual 14 ...

Страница 23: ...Users Manual 15 ...

Страница 24: ...Users Manual 16 ...

Страница 26: ...Users Manual 18 5 2 Register Map ...

Страница 27: ...Users Manual 19 ...

Страница 28: ...Users Manual 20 ...

Страница 30: ...Users Manual 22 5 3 2 PIO2 and PIO1 ...

Страница 32: ...Users Manual 24 5 3 4 Connection of external bus master 5 3 5 INT 7 0 active status clear ...

Страница 33: ...Users Manual 25 5 3 6 INT 7 0 active status set up ...

Страница 34: ...Users Manual 26 ...

Страница 123: ...TOSHIBA TMPR3904F Rev 2 0 115 26 ...

Страница 169: ...TOSHIBA TMPR3904F Rev 2 0 161 26 ...

Страница 203: ...TOSHIBA TMPR3904F Rev 2 0 195 ...

Страница 230: ......