19

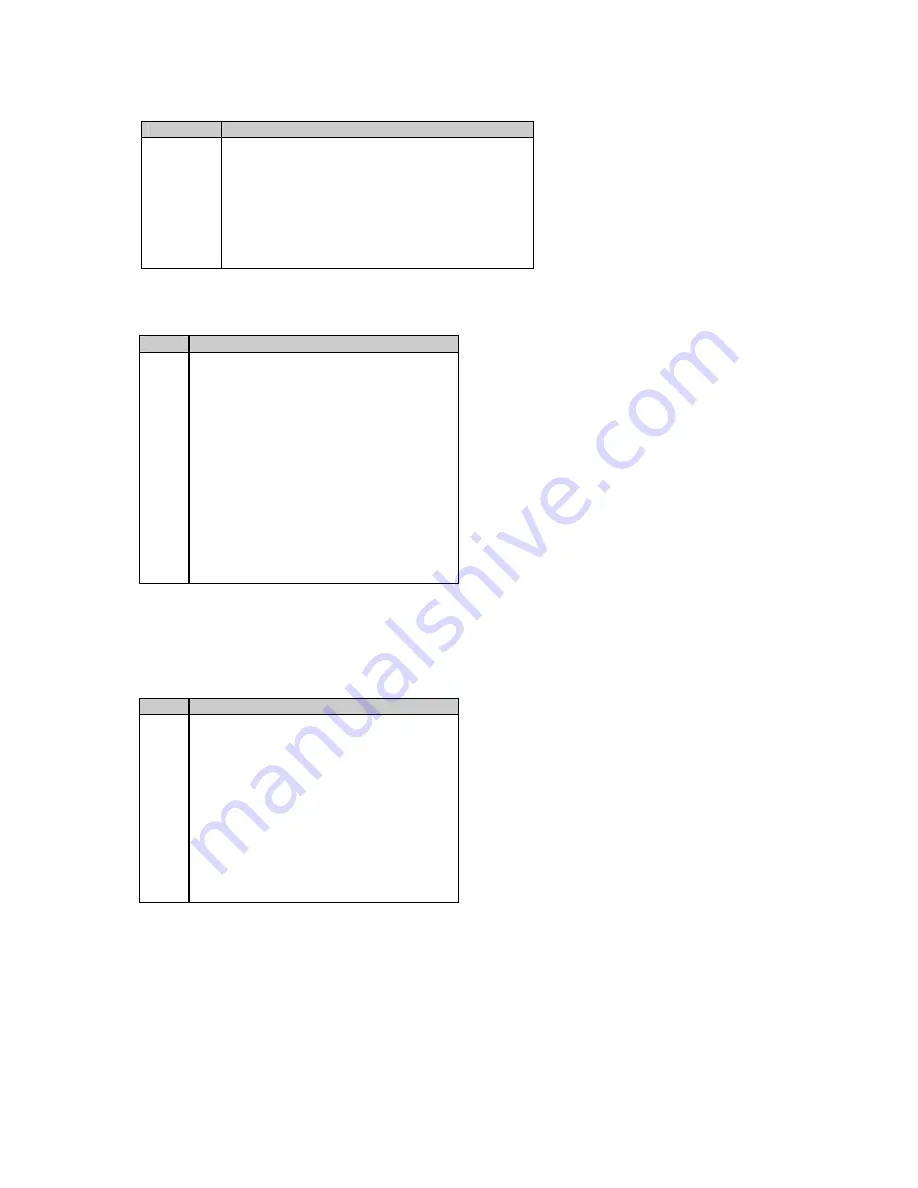

Table 5-14 Data Log Status

Bit

Description

0

New data log #1

1

New data log #2

2

New data log #3

3

New data log #4

4

New data log #5

5

New data log #6

6

New data log #7

7

New data log #8

4-15

Not used (permanently set to 0)

Bit meaning: 0 = no new logs, 1 = new log recorded (the new log flag is reset when the user reads the first log

record after the flag has been set)

Table 5-15 Setpoint Alarm Status

Bit

Description

0 Alarm

#1

1 Alarm

#2

2 Alarm

#3

3 Alarm

#4

4 Alarm

#5

5 Alarm

#6

6 Alarm

#7

7 Alarm

#8

8 Alarm

#9

9 Alarm

#10

10 Alarm

#11

11 Alarm

#12

12 Alarm

#13

13 Alarm

#14

14 Alarm

#15

15 Alarm

#16

Bit meaning: 1 = setpoint has been operated

The setpoint alarm register stores the status of the operated setpoints by setting the appropriate bits to 1. The

alarm status bits can be reset all together by writing zero to the setpoint alarm register. It is possible to reset

each alarm status bit separately by writing back the contents of the alarm register with a corresponding alarm bit

set to 0.

Table 5-16 Self-check Alarm Status

Bit

Description

0 Reserved

1 ROM

error

2 RAM

error

3

Watchdog timer reset

4 Sampling

failure

5

Out of control trap

6 Reserved

7 Timing

failure

8

Loss of power (power up)

9

External reset (warm restart)

10 Configuration

corrupted

11

RTC time-synchronization required

12-15 Reserved

The self-check alarm register indicates possible problems with the instrument hardware or setup configuration.

The hardware problems are indicated by the appropriate bits which are set whenever the instrument fails self-test

diagnostics or in the event of loss of power. The setup configuration problems are indicated by the dedicated bit

which is set when either configuration register is corrupted. In this event, the instrument will use the default

configuration. The configuration corrupt bit may also be set as a result of the legal changes in the setup

configuration since the instrument might implicitly change or clear other setups if they are affected by the

changes made.

Hardware fault bits can be reset by writing zero to the self-check alarm register. The configuration corrupt status

bit and RTC synchronization bit are also reset automatically when you change setup or update RTC either via the

front panel or through communications.