Saia-Burgess

Controls Ltd.

Hardware Manual for the PCD3 Series│Document 26/789; Version E 5│31.01.2005

Hardware

PCD3.H150

5-83

5

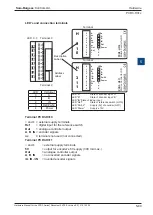

Block diagram

For more details, please refer to manual 26/761, “PCD2.H150 - SSI-Interface for

absolute encoder”

Watchdog: This module cannot be used on the base address 240 because it would

interact with the watchdog, which would cause malfunction.

Please refer to the

“Watchdog”

section for details on how to use the watchdog

correctly together with PCD3 components.

CLK

/CLK

D

/D

A 12

A 13

User PROM

FPGA

(Field Programmable

Gate Array)

PCD bus

Input filter and adaptation 24 V...5 V

Output amplifier 5...32 VDC (Uext)

Clock

/Clock

Data

/Data

Output 12

A 14

A 15

Output 13

Output 14

Output 15

i