Connector Pin Assignments A-9

IDE INTERFACE CONNECTORS

All signal levels in the IDE interface are TTL compatible. A logic 1 is a signal whose

voltage level is between 2.0 and 5.0 V. A logic 0 is a signal measuring between 0.00 V and

0.70 V.

The two system board PCI/IDE connectors are physically identical. Electrically the primary

IDE connector uses IRQ14 and the secondary IDE connector uses IRQ15. Table A-12

provides the IDE pin assignments. All signals on the Host interface have the prefix HOST.

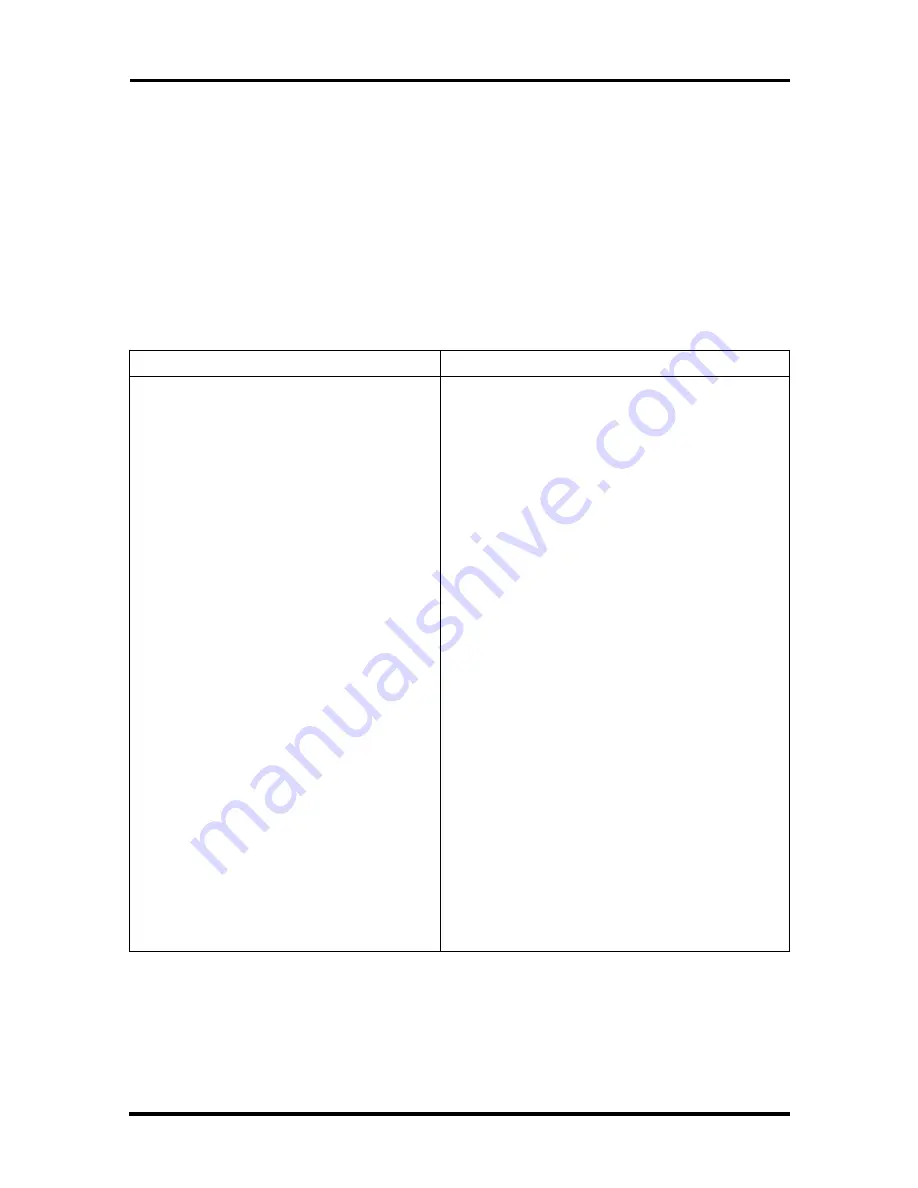

Table A-12 IDE Connector Pin Assignments

Pin

Signal

Pin

Signal

01

HOST RESET

02

GND

03

HOST DATA 7

04

HOST DATA 8

05

HOST DATA 6

06

HOST DATA 9

07

HOST DATA 5

08

HOST DATA 10

09

HOST DATA 4

10

HOST DATA 11

11

HOST DATA 3

12

HOST DATA 12

13

HOST DATA 2

14

HOST DATA 13

15

HOST DATA 1

16

HOST DATA 14

17

HOST DATA 0

18

HOST DATA 15

19

GND

20

KEY

21

DRQ3

22

GND

23

HOST IOW

24

GND

25

HOST IOR

26

GND

27

IOCHRDY

28

HOST ALE

29

DACK3

30

GND

31*

HOST IRQ14

32

HOST IO16

33

HOST ADDR 1

34

GND

35

HOST ADDR 0

36

HOST ADDR 2

37

HOST CSO

38

HOST CS1

39

HOST SLV/ACT

40

GND

*The secondary IDE connector uses IRQ15

Содержание POWERMATE P2166

Страница 217: ...Index 4 ...