January 2007

233

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

Intel

®

6300ESB Design Guidelines

For more information on General Purpose Event (GPE) Register recommendations for Microsoft

Windows

*

operating systems refer to the document GPE Routing for Microsoft Windows, which

can be found at

http://www.microsoft.com/whdc/hwdev/tech/onnow/GPE_routing.mspx

9.11

RTC

The 6300ESB contains a real time clock (RTC) with 256 bytes of battery backed SRAM. The

internal RTC module provides two key functions: keeping date and time and storing system data in

its RAM when the system is powered down.

The 6300ESB uses a crystal circuit to generate a low-swing 32 KHz input sine wave. This input is

amplified and driven back to the crystal circuit through the RTCX2 signal. Internal to the

6300ESB, the RTCX1 signal is amplified to drive internal logic as well as generate a free running

full swing clock output for system use. This output ball of the 6300ESB is called SUSCLK. This is

illustrated in

.

For further information on the RTC, consult Application Note AP-728 ICH Family Real Time

Clock (RTC) Accuracy and Considerations Under Test Conditions

. This application note is valid

for the 6300ESB.

Even when the 6300ESB internal RTC is not used, it is still necessary to supply a clock input to

RTCX1 of the platform because other signals are gated off that clock in suspend modes. However,

in this case, the frequency accuracy (32.768 KHz) of the clock inputs is not critical; a crystal may

be used or a single clock input may be driven into RTCX1with RTCX2 left as no connect, as shown

in

.

Note:

This is not a validated feature on 6300ESB. Please note that the peak-to-peak swing on RTCX1

may not exceed 2.0 V.

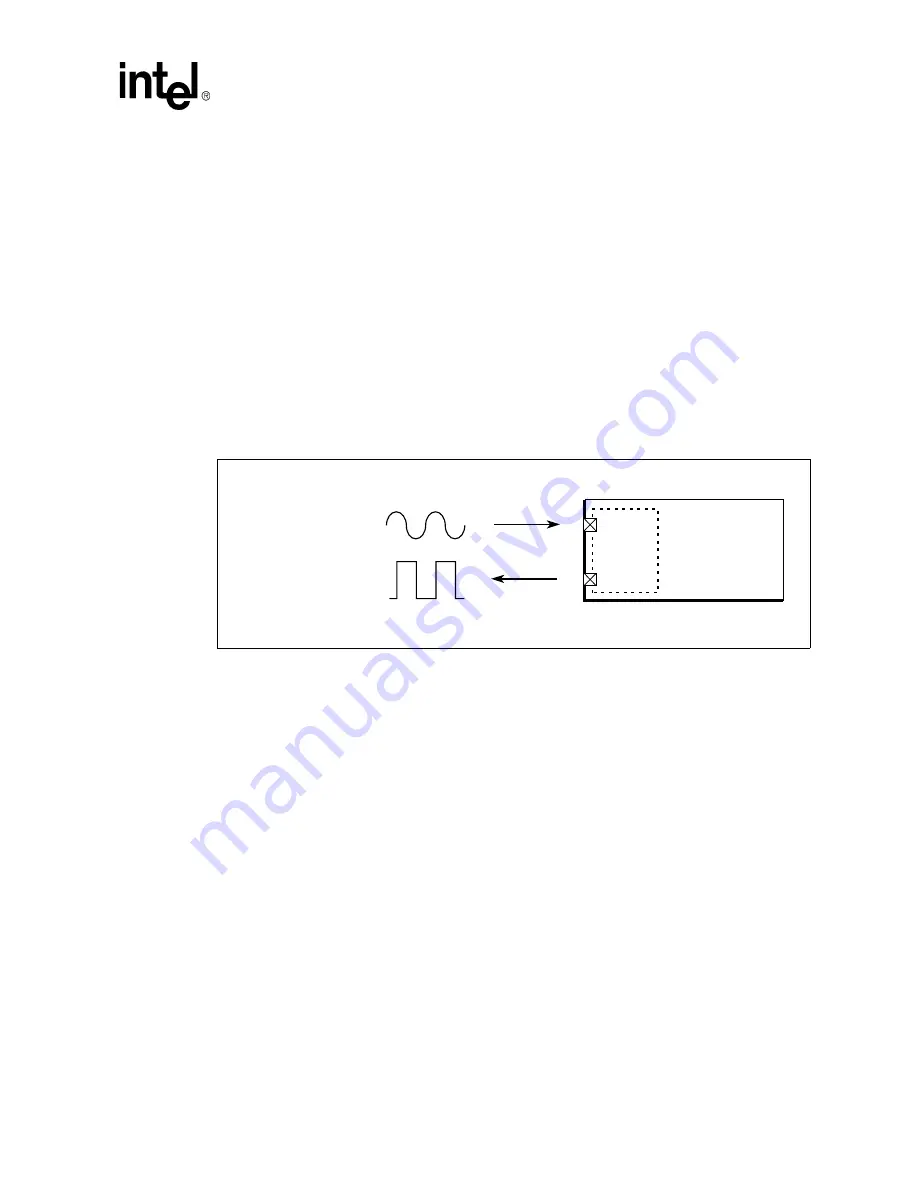

Figure 127.

RTCX1 and SUSCLK Relationship in 6300ESB

B1180-02

Internal

Oscillator

Low-Swing 32.768 kHz

Sine Wave Source

Full-Swing 32.768 kHz

Output Signal

Intel

®

6300ESB

I/O Controller

Hub

RTCX1

SUSCLK

Содержание 6300ESB ICH

Страница 24: ...24 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Introduction...

Страница 36: ...36 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide General Design Considerations...

Страница 102: ...102 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide...

Страница 122: ...122 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide...

Страница 152: ...152 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide System Memory Design Guidelines DDR SDRAM...

Страница 172: ...172 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Integrated Graphics Display Port...

Страница 190: ...190 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Hub Interface...

Страница 246: ...246 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Intel 6300ESB Design Guidelines...

Страница 264: ...264 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Platform Clock Routing Guidelines...

Страница 298: ...298 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Schematic Checklist Summary...

Страница 318: ...318 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Layout Checklist...