AP08056

Power Saving Features

Operating on a Lower Frequency Clock Mode

Application Note

19

V1.0, 2006-12

6.1

Device Clock in PLL Base Mode

In the PLL base mode, the oscillator is disconnected from the PLL and the system

frequency is derived from the VCO base (free running) frequency clock divided by the K

factor:

The ranges of the VCO base frequency is shown in

The VCO base frequency of different devices will range between 10 MHz to 80 MHz

depending on the VCOSEL setting. Users will need to manually check the system

frequency of each device by outputting the device’s system clock at the CLKOUT pin.

The code example to output the system clock is as follows:

SCU_PAGE = 0x01;

//open SCU page 1 to access COCON

COCON = 0x37;

//select clock output frequency/10

PORT_PAGE = 0x02;

//open port page 2 to access Px_ALTSELx

P0_ALTSEL0 = 0x01;

//select clock out function for P0.0

P0_ALTSEL1 = 0x00;

PORT_PAGE = 0x00;

//open port page 0 to access Px_DIR

P0_DIR = 0x01;

//set P0.0 as output port

At the output of P0.0, the clock output frequency is half of the frequency that is chosen

by the bitfield COCON.COREL. In the above example, the system clock output at P0.0

has been divided by a factor of 10 based on the setting of the bitfield COCON.COREL.

The system frequency can hence be obtained by multiplying the measured frequency by

a factor of 20.

Users must take note that the VCO base frequency that was determined could vary

approximately up to +/- 10% depending on the stability of the power supply to the PLL

(i.e. power supply from EVR) and the temperature.

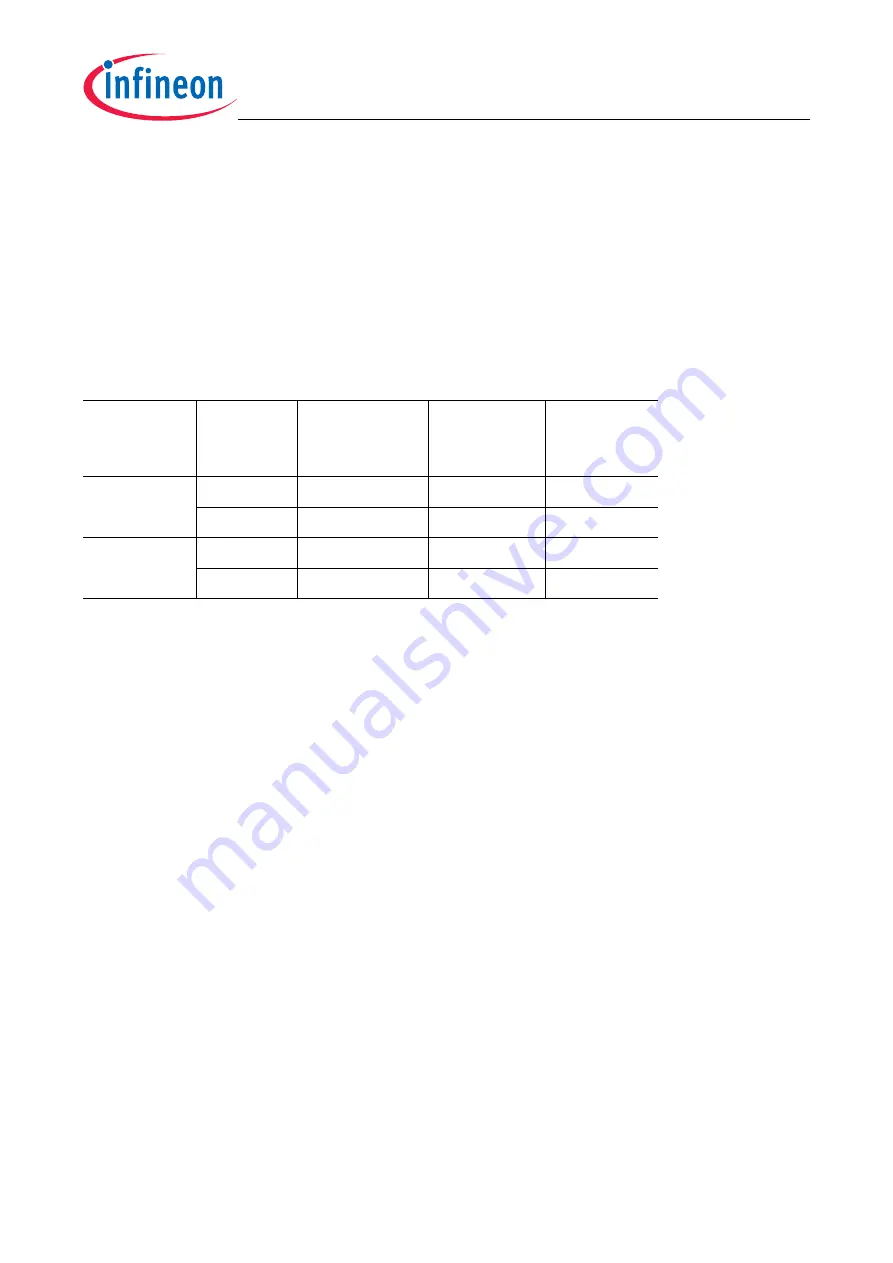

Table 11

VCO base (f

VCObase)

and system frequency (f

SYS

) ranges

Device

VCOSEL f

VCObase

Range (MHz)

f

SYS

Range

when K = 1

(MHz)

f

SYS

Range

when K = 2

(MHz)

XC866

0

10 - 80

-

5 - 40

1

20 - 80

-

10 - 40

XC886/888

0

20 - 80

20 - 80

10 - 40

1

10 - 80

10 - 80

5 - 40

f

SYS

1

K

---- f

VCObase

⋅

=