User’s Manual

3-5

05.99

Memory Organization

C513AO

3.5

Special Function Registers

The registers reside in the special function register area, with the exception of the Program Counter

and the four General Purpose Register banks. The special function register area consists of two

portions: the

standard

special function register area and the

mapped

special function register area.

Four special function registers of the C513AO (PCON1, VR0, VR1 & VR2) are located in the

mapped special function register area. For accessing the mapped special function register area, bit

RMAP in special function register SYSCON must be set. All other special function registers of the

C513AO are located in the standard special function register area.

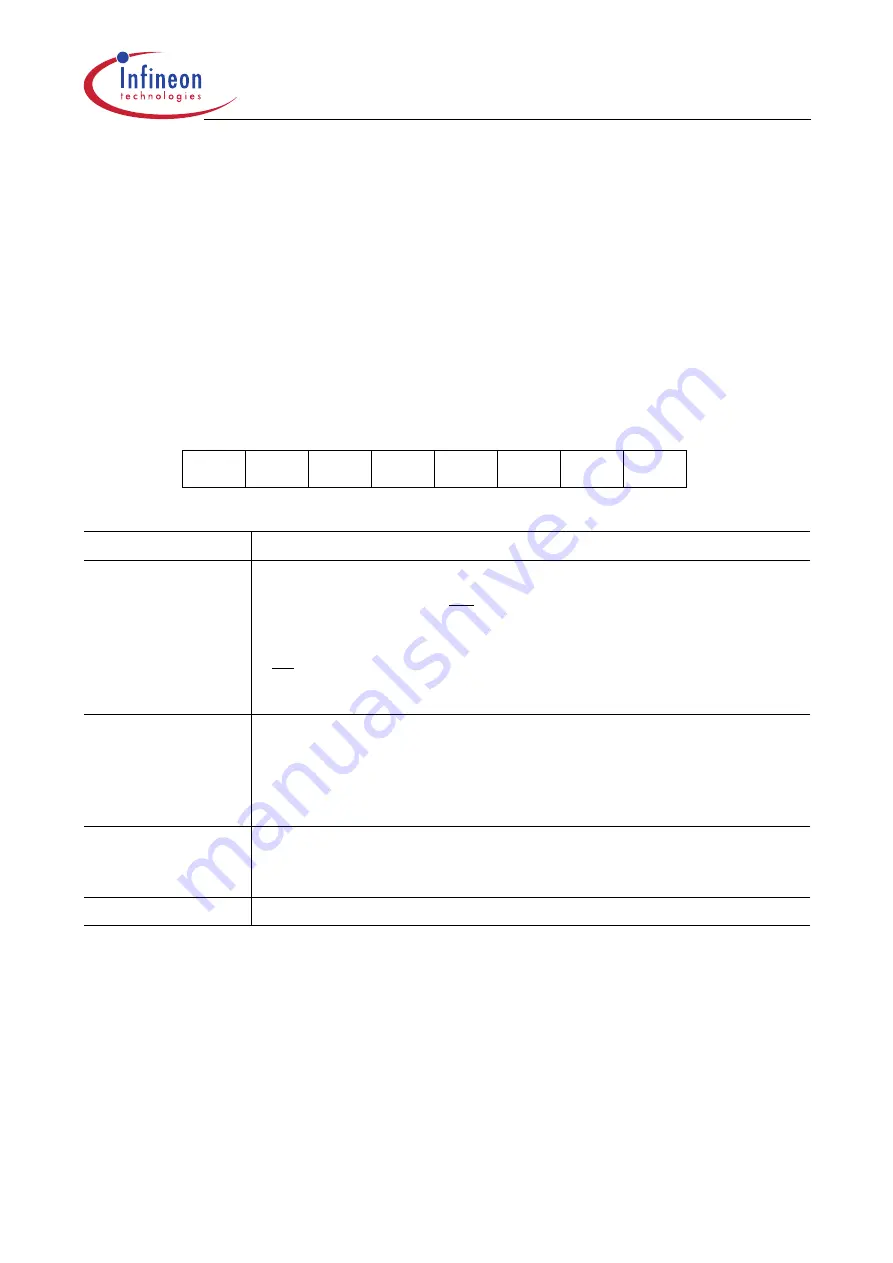

Special Function Register SYSCON (Address B1

H

)

Reset Value: XX10XXX0

B

If bit RMAP is set, mapped special function registers can be accessed. This bit is not cleared by

hardware automatically.

The forty Special Function Registers (SFRs) in the standard and mapped SFR area include pointers

and registers that provide an interface between the CPU and the other on-chip peripherals. The

SFRs of the C513AO are listed in Table 3-1 and Table 3-2. In Table 3-1, they are organized in

groups which refer to the functional blocks of the C513AO. Table 3-2 illustrates the contents of the

SFRs in numeric order of their addresses.

Bit

Function

EALE

Enable ALE Output

EALE = 0: ALE generation is disabled during internal code memory

accesses (EA = 1) ; ALE is generated during MOVX

instructions.

EALE = 1: ALE generation is enabled.

If EA = 0, the ALE generation is always enabled and the bit EALE has no

effect on ALE generation.

RMAP

Special function Register MAP bit

RMAP = 0: The access to the non-mapped (standard) special function

register area is enabled.

RMAP = 1: The access to the mapped special function register area is

enabled.

XMAP

Global XRAM MAP access enable/disable control

XMAP = 0: On-chip XRAM disabled (default after reset).

XMAP = 1: On-chip XRAM enabled.

–

Reserved for future use. Read by CPU; returns undefined values.

7

6

5

4

3

2

1

0

EALE

RMAP

–

B1

H

SYSCON

Bit No.

MSB

LSB

–

–

–

–

XMAP