Rev. 1.00

64

August 29, 2018

Rev. 1.00

65

August 29, 2018

HT45F6530

AC Voltage Regulator Flash MCU

HT45F6530

AC Voltage Regulator Flash MCU

Bit 2~0

CTnRP2~CTnRP0

: CTMn CCRP 3-bit register, compared with the CTMn counter

bit 9~bit 7

Comparator P match period=

0: 1024 CTMn clocks

1~7: (1~7)×128 CTMn clocks

These three bits are used to setup the value on the internal CCRP 3-bit register, which

are then compared with the internal counter’s highest three bits. The result of this

comparison can be selected to clear the internal counter if the CTnCCLR bit is set to

zero. Setting the CTnCCLR bit to zero ensures that a compare match with the CCRP

values will reset the internal counter. As the CCRP bits are only compared with the

highest three counter bits, the compare values exist in 128 clock cycle multiples.

Clearing all three bits to zero is in effect allowing the counter to overflow at its

maximum value.

• CTMnC1 Register

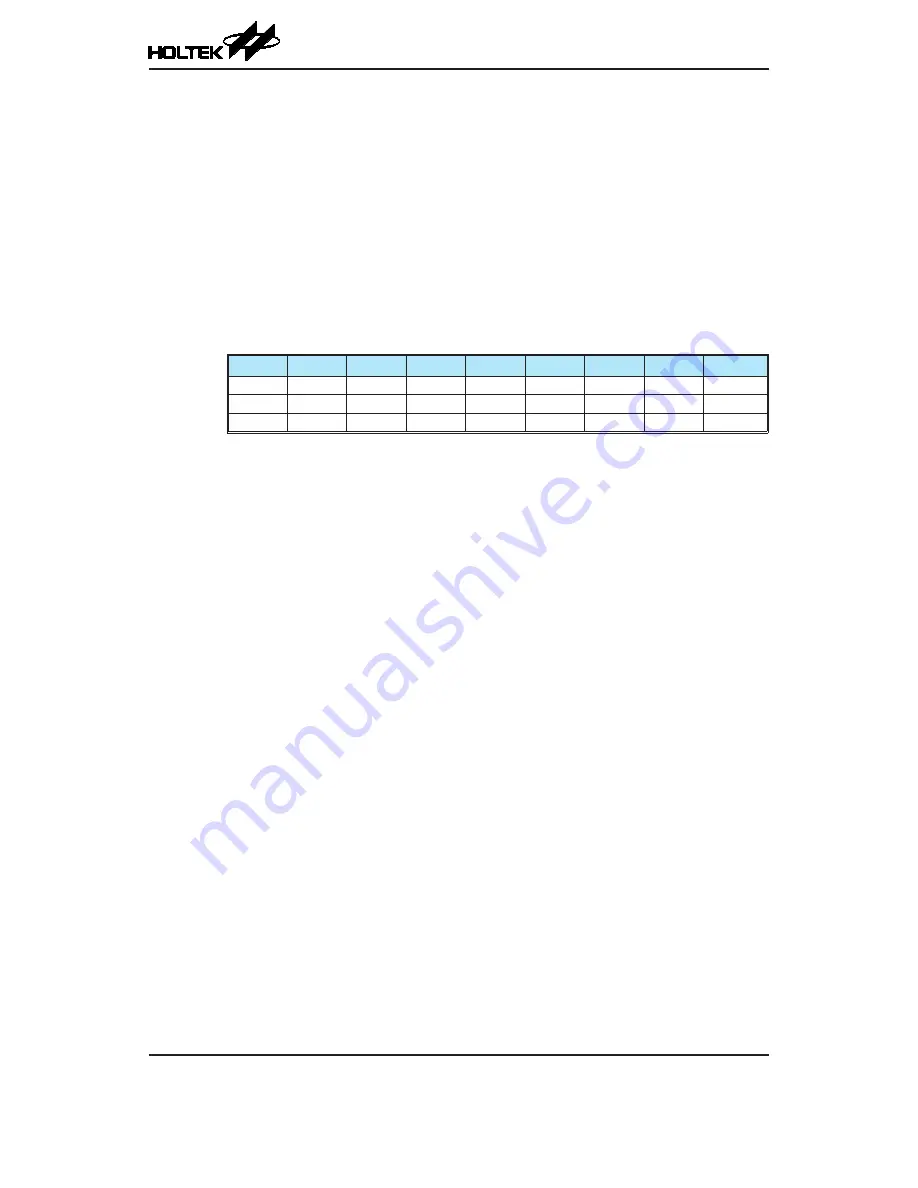

Bit

7

6

5

4

3

2

1

0

Name

CTnM1

CTnM0

CTnIO1

CTnIO0

CTnOC

CTnPOL CTnDPX CTnCCLR

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

0

0

0

0

0

0

Bit 7~6

CTnM1~CTnM0

: Select CTMn Operating Mode

00: Compare Match Output Mode

01: Undefined

10: PWM Output Mode

11: Timer/Counter Mode

These bits setup the required operating mode for the CTMn. To ensure reliable

operation the CTMn should be switched off before any changes are made to the

CTnM1 and CTnM0 bits. In the Timer/Counter Mode, the CTMn output pin state is

undefined.

Bit 5~4

CTnIO1~CTnIO0

: Select CTMn external pin CTPn function

Compare Match Output Mode

00: No change

01: Output low

10: Output high

11: Toggle output

PWM Output Mode

00: PWM output inactive state

01: PWM output active state

10: PWM output

11: Undefined

Timer/Counter Mode

Unused

These two bits are used to determine how the CTMn external pin changes state when a

certain condition is reached. The function that these bits select depends upon in which

mode the CTMn is running.

In the Compare Match Output Mode, the CTnIO1 and CTnIO0 bits determine how the

CTMn output pin changes state when a compare match occurs from the Comparator A.

The CTMn output pin can be setup to switch high, switch low or to toggle its present

state when a compare match occurs from the Comparator A. When the bits are both

zero, then no change will take place on the output. The initial value of the CTMn

output pin should be setup using the CTnOC bit in the CTMnC1 register. Note that

the output level requested by the CTnIO1 and CTnIO0 bits must be different from the

initial value setup using the CTnOC bit otherwise no change will occur on the CTMn

output pin when a compare match occurs. After the CTMn output pin changes state,

it can be reset to its initial level by changing the level of the CTnON bit from low to

high.