Rev. 1.00

72

August 29, 2018

Rev. 1.00

73

August 29, 2018

HT45F6530

AC Voltage Regulator Flash MCU

HT45F6530

AC Voltage Regulator Flash MCU

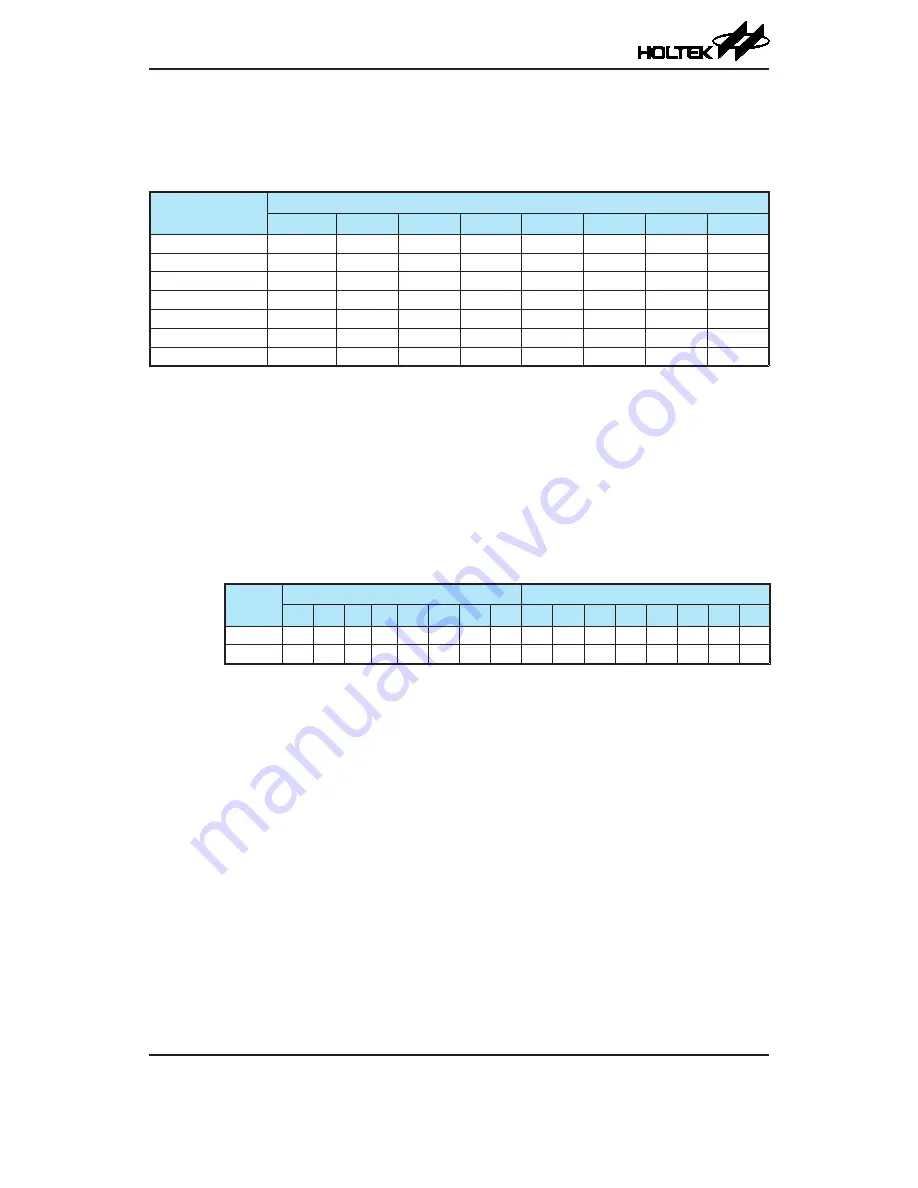

A/D Converter Register Description

Overall operation of the A/D converter is controlled using several registers. A read only register pair

exists to store the A/D converter data 12-bit value. The remaining three registers are control registers

which setup the operating and control function of the A/D converter.

Register Name

Bit

7

6

5

4

3

2

1

0

SADOL (ADRFS=0)

D3

D2

D1

D0

—

—

—

—

SADOL (ADRFS=1)

D7

D6

D5

D4

D3

D2

D1

D0

SADOH (ADRFS=0)

D11

D10

D9

D8

D7

D6

D5

D4

SADOH (ADRFS=1)

—

—

—

—

D11

D10

D9

D8

SADC0

START

ADBZ

ADCEN

ADRFS

SACS3

SACS2

SACS1

SACS0

SADC1

SAINS3

SAINS2

SAINS1

SAINS0

—

SACKS2 SACKS1 SACKS0

SADC2

ADPGAEN

—

—

PGAIS

SAVRS1 SAVRS0 PGAGS1 PGAGS0

A/D Converter Register List

A/D Converter Data Registers – SADOL, SADOH

As this device contains an internal 12-bit A/D converter, it requires two data registers to store the

converted value. These are a high byte register, known as SADOH, and a low byte register, known

as SADOL. After the conversion process takes place, these registers can be directly read by the

microcontroller to obtain the digitised conversion value. As only 12 bits of the 16-bit register space

is utilised, the format in which the data is stored is controlled by the ADRFS bit in the SADC0

register as shown in the accompanying table. D0~D11 are the A/D conversion result data bits. Any

unused bits will be read as zero. Note that A/D data registers contents will be unchanged if the A/D

converter is disabled.

ADRFS

SADOH

SADOL

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

0

D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

0

0

0

0

1

0

0

0

0 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

A/D Converter Data Registers

A/D Converter Control Registers – SADC0, SADC1, SADC2

To control the function and operation of the A/D converter, three control registers known as

SADC0~SADC2 are provided. These 8-bit registers define functions such as the selection of which

analog signal is connected to the internal A/D converter, the digitised data format, the A/D clock

source as well as controlling the start function and monitoring the A/D converter busy status. As the

device contains only one actual analog to digital converter hardware circuit, each of the external

or internal analog signal inputs must be routed to the converter. The SACS3~SACS0 bits in the

SADC0 register are used to determine which external channel input is selected to be converted.

The SAINS3~SAINS0 bits in the SADC1 register are used to determine that the analog signal to be

converted comes from the internal analog signal or external analog channel input. The A/D converter

also contains a programmable gain amplifier, PGA, to generate the A/D converter internal reference

voltage. The overall operation of the PGA is controlled using the SADC2 register.

The relevant pin-shared function selection bits determine which pins on I/O Ports are used as analog

inputs for the A/D converter input and which pins are not to be used as the A/D converter input.

When the pin is selected to be an A/D input, its original function whether it is an I/O or other pin-

shared function will be removed. In addition, any internal pull-high resistor connected to the pin will

be automatically removed if the pin is selected to be an A/D converter input.